### OPERAND-OPTIMIZED ASYNCHRONOUS FLOATING-POINT ARITHMETIC CIRCUITS

A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by Basit Riaz Sheikh January 2012 © 2012 Basit Riaz Sheikh ALL RIGHTS RESERVED

### OPERAND-OPTIMIZED ASYNCHRONOUS FLOATING-POINT ARITHMETIC CIRCUITS

Basit Riaz Sheikh, Ph.D.

Cornell University 2012

Fast floating-point computations are critical in a wide range of applications. Today, the performance of these applications is limited by power constraints. The traditional power reduction schemes, which relied primarily on technology and voltage scaling, are not sufficient any more. In this thesis, we propose two novel asynchronous pipeline templates and multiple operand-dependent optimization techniques to significantly reduce the overall power consumption while preserving the average throughput.

Our novel pipeline templates reduce power consumption by minimizing the handshake circuitry and employing single-track handshake protocol. Noise and timing robustness constraints of our pipelined circuits are quantified across all process corners. A completion detection scheme based on wide NOR gates is presented, which results in significant latency and energy savings especially as the number of output tokens increase.

Furthermore, this thesis presents novel operand-dependent optimization techniques to improve the energy efficiency of IEEE-754 compliant floatingpoint adder and floating-point multiplier designs. Some of these optimizations are highly challenging, if at all possible, in a synchronous design because they increase the worst case critical path but on average have negligible impact on performance. To our knowledge, this is the first detailed design of highperformance asynchronous floating-point adder and floating-point multiplier.

## **Biographical Sketch**

Basit Riaz Sheikh was born in Lahore, Pakistan. He joined the prestigious Aitchison College in Lahore in 1989, where he completed 12 years of his primary, middle, and high school education. He secured first position in his class in the *O-Level* examination of 1999. Due to his exceptional academic and extracurricular record, Basit was appointed the *Head Boy* of the entire student body comprising over two thousand students.

In the fall of 2001, Basit joined the National University of Singapore on *presidential scholarship* to pursue his undergraduate studies in Electrical Engineering. In 2002, he transferred to the University of Texas at Austin where he developed great interest in VLSI chip design. Basit graduated from the University of Texas in 2005 with B.S. in Electrical Engineering with highest honors.

Basit has been enrolled in the M.S. / Ph.D. program in the school of Electrical and Computer Engineering at Cornell University since August 2005. At Cornell, his research has primarily focused on energy-efficient VLSI chip design, arithmetic circuits, and computer architecture. Over the years, Basit gained invaluable industry experience while working at Applied Materials Inc., National Instruments Inc., and Intel Corporation in various positions ranging from software development to hardware design engineer. He is a member of Professor Rajit Manohar's Asynchronous VLSI lab. For mom and papa

### Acknowledgements

First of all, I would like to extend utmost gratitude to my advisor, Professor Rajit Manohar, who has been a great source of inspiration and guidance throughout my graduate studies. He encouraged me to explore unconventional ideas and helped a great deal in refining those into a cohesive research. Whenever I got stuck in my research, he came to my aid and pointed me in the right direction. It has been a great learning experience working under his supervision.

I would like to thank Professor David Albonesi for his guidance in the first few years of my graduate studies at Cornell and for taking keen interest in my progress throughout. I owe my gratitude to Professor Brian Evans and Professor Yale Patt at the University of Texas-Austin for encouraging me to pursue a PhD. They provided the motivation for what has been an intellectually stimulating and enlightening journey.

I want to thank all of my friends for supporting me during the rough and challenging phases of my PhD. Special thanks to Carlos Tadeo and Filipp Akopyan for their technical assistance with tool-flow infrastructure. I want to thank Paula Petrica for her endearing friendship and making six years in Ithaca a truly memorable experience.

My greatest gratitude to my family for their endless love and support. If it wasn't for their unflinching faith in me none of this would have been possible.

# **Table of Contents**

|   | Biographical Sketch                                          | iii  |

|---|--------------------------------------------------------------|------|

|   | Dedication                                                   | iv   |

|   | Acknowledgements                                             | v    |

|   | Table of Contents                                            | vi   |

|   | List of Tables                                               | ix   |

|   | List of Figures                                              | x    |

|   | List of Abbreviations                                        | xiii |

| 1 | Introduction                                                 | 1    |

|   | 1.1 Motivation                                               | 1    |

|   | 1.2 Operand Dependent Floating-Point Unit Design             | 3    |

|   | 1.3   Asynchronous Circuit Design                            | 5    |

|   | 1.4 Thesis Contribution and Organization                     | 6    |

| 2 | Background                                                   | 8    |

|   | 2.1 Floating-Point Computations                              | 8    |

|   | 2.1.1 IEEE Floating-Point Standard                           | 9    |

|   | 2.1.2 Floating-Point Adder                                   | 11   |

|   | 2.1.3 Floating-Point Multiplier                              | 13   |

|   | 2.2 Floating-Point Application Benchmarks                    | 16   |

|   | 2.3 Related Work                                             | 19   |

|   | 2.3.1 Asynchronous Arithmetic                                | 19   |

|   | 2.3.2 Synchronous Floating-Point Adders and Multipliers      | 21   |

|   | 2.4 Asynchronous Pipelines                                   | 23   |

|   | 2.4.1 Quasi-Delay-Insensitive Circuits                       | 23   |

|   | 2.4.2 Fine-grain bundled-data pipelines                      | 28   |

| 3 | Energy-Efficient Pipeline Design                             | 30   |

|   | 3.1 Improving Energy-Efficiency of Fine-Grain Pipelines      | 31   |

|   | 3.1.1 Four phase handshake vs. Single-track handshake        | 33   |

|   | 3.1.2 Relative Path Timing Assumption                        | 34   |

|   | 3.2 High Throughput Energy Efficient Pipeline Templates      | 35   |

|   | 3.2.1 N-P and N-Inverter Pipeline Templates                  | 35   |

|   | 3.2.2 Completion detection logic for large number of outputs | 42   |

|   |      | 3.2.3 Conversion Templates                     | 46  |

|---|------|------------------------------------------------|-----|

|   | 3.3  | Design Considerations and Trade-offs           | 49  |

|   |      | 3.3.1 Completion Detection Circuits            | 49  |

|   |      | 3.3.2 Throughput, Energy, and Area Trade-offs  | 52  |

|   |      | 3.3.3 Noise Analysis                           | 55  |

|   |      | 3.3.4 Timing Margin                            | 58  |

|   | 3.4  | 8x8 Booth-Encoded Array Multiplier             | 61  |

|   |      | 3.4.1 Evaluation of 8x8-bit Multiplier Designs | 66  |

|   | 3.5  | Summary                                        | 72  |

| 4 | An   | Operand-Optimized Floating-Point Adder         | 73  |

|   | 4.1  | A Baseline Asynchronous FPA                    | 74  |

|   |      | 4.1.1 Fine-grain Asynchronous Pipelining       | 74  |

|   |      | 4.1.2 Hybrid Kogge-Stone Carry-Select Adder    | 76  |

|   |      | 4.1.3 Leading One Prediction and Decoding      | 78  |

|   |      | 4.1.4 Evaluation of Baseline Asynchronous FPA  | 78  |

|   |      | 4.1.5 Power Breakdown and Analysis             | 80  |

|   | 4.2  | Coarse-Grain Power Reduction                   | 81  |

|   |      | 4.2.1 Interleaved Asynchronous Adder           | 83  |

|   |      | 4.2.2 Left or Right Pipeline                   | 85  |

|   | 4.3  | Operand-Based Optimizations                    | 86  |

|   |      | 4.3.1 Two-Way Right-Align Shift                | 86  |

|   |      | 4.3.2 Minimizing LOP Logic                     | 91  |

|   |      | 4.3.3 Post-Add Right Pipeline                  | 93  |

|   |      | 4.3.4 Zero-input Operands                      | 96  |

|   | 4.4  | Evaluation of Operand-Optimized FPA            | 99  |

|   | 4.5  | Summary                                        | 106 |

| 5 | Floa | ating-Point Multiplication                     | 107 |

|   | 5.1  |                                                | 107 |

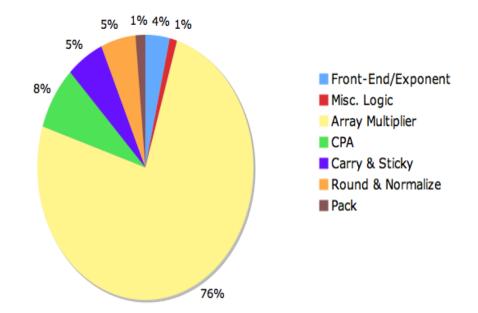

|   | 5.2  | Power Breakdown and Analysis                   |     |

|   | 5.3  | Multiplier Design Trade-offs                   |     |

|   |      | 5.3.1 Iterative Multipliers                    |     |

|   |      |                                                | 113 |

|   | 5.4  |                                                | 117 |

|   |      |                                                | 117 |

|   |      | 1 0                                            | 120 |

|   | 5.5  | 5 0 5 1 0                                      | 126 |

|   |      |                                                | 127 |

|   | _    | 5 1 0                                          | 130 |

|   | 5.6  |                                                | 132 |

|   |      |                                                | 136 |

|   |      | 5.6.2 Underflow Output                         |     |

|   |      | 5.6.3 Denormal/Underflow: Unified Rounding     | 140 |

|     | 5.7   | 5.6.4 Zero-input Operands     |                   |

|-----|-------|-------------------------------|-------------------|

| 6   |       | <b>clusion</b><br>Future Work | <b>149</b><br>152 |

| Bil | oliog | raphy                         | 153               |

# List of Tables

| 3.1 | 8x8-bit Array Multiplier Latency          |

|-----|-------------------------------------------|

| 3.2 | 8x8-bit Array Multiplier Transistor Count |

| 4.1 | Throughput across different carry lengths |

| 4.2 | Optimized FPA Energy & Throughput         |

| 4.3 | Optimized FPA 2-WCHB Zero Bypass          |

| 4.4 | Optimized FPA Latency                     |

| 4.5 | Leakage Power                             |

| 4.6 | Comparison to other FPAs and FMAs         |

| 5.1 | Array Multiplier                          |

| 5.2 | Asynchronous FPM vs Synchronous FPM       |

| 5.3 | Zero Operand Features                     |

# **List of Figures**

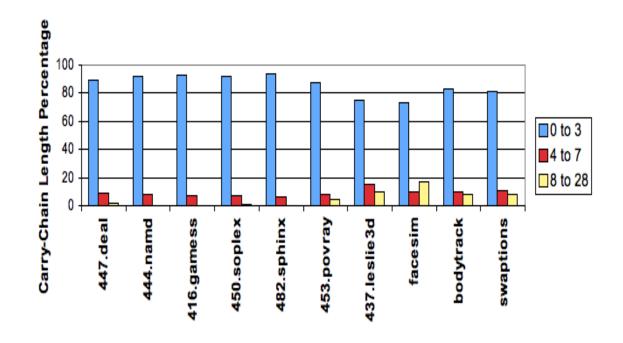

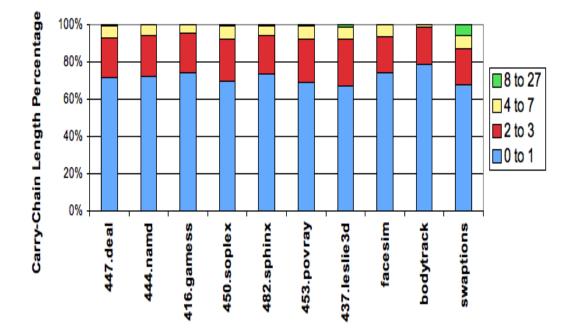

| 1.1  | Longest carry-chain length in a 56-bit Adder                         | 4  |

|------|----------------------------------------------------------------------|----|

| 2.1  | Double precision floating-point format                               | 10 |

| 2.2  | Floating-point Adder Datapath                                        | 12 |

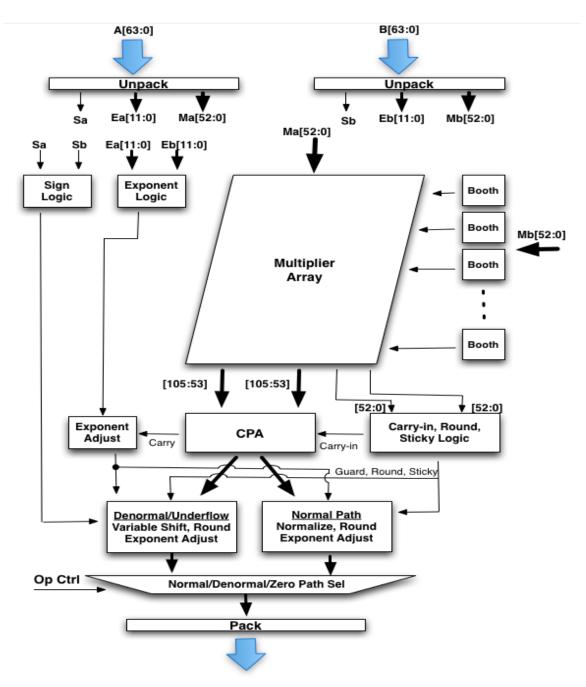

| 2.3  | Floating-point Multiplier Datapath                                   | 15 |

| 2.4  | Asynchronous pipelines: sender-receiver handshake protocol           | 24 |

| 2.5  | A WCHB pipeline stage                                                | 25 |

| 2.6  | A two input and one output PCeHB template                            | 26 |

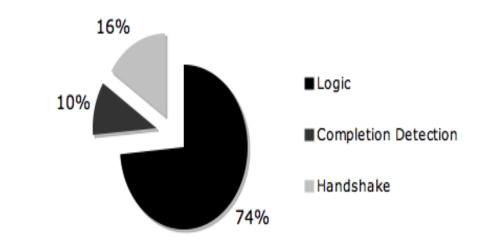

| 2.7  | Power breakdown of a full-adder circuit in a PCeHB pipeline          | 29 |

| 3.1  | Single-track handshake protocol                                      | 34 |

| 3.2  | N-P pipeline template                                                | 36 |

| 3.3  | Ack signals to ensure correctness                                    | 40 |

| 3.4  | N-Inverter pipeline template                                         | 43 |

| 3.5  | Multi-stage c-element tree completion detection logic for large      |    |

|      | number of outputs                                                    | 44 |

| 3.6  | Completion detection logic for large number of outputs               | 45 |

| 3.7  | Four-phase protocol to single-track protocol conversion tem-         |    |

|      | plate                                                                | 47 |

| 3.8  | Single-track protocol to four-phase protocol conversion template     | 48 |

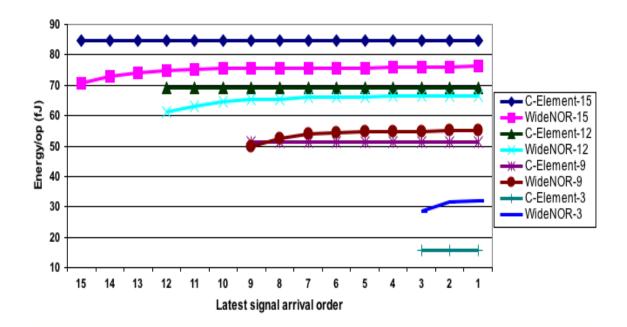

| 3.9  | Latency comparison of completion detection schemes                   | 50 |

| 3.10 | Completion detection energy consumption for different arrival        |    |

|      | order of chosen signal                                               | 51 |

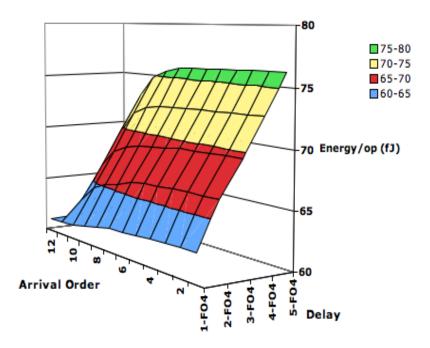

| 3.11 | WideNOR for 12-outputs with varying delay of latest signal           | 52 |

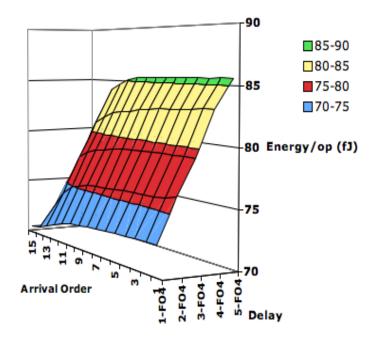

| 3.12 | WideNOR for 15-outputs with varying delay of latest signal           | 53 |

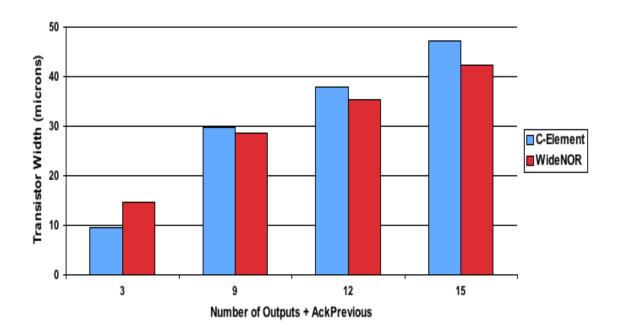

| 3.13 | C-Element vs WideNOR: total transistor width comparison              | 54 |

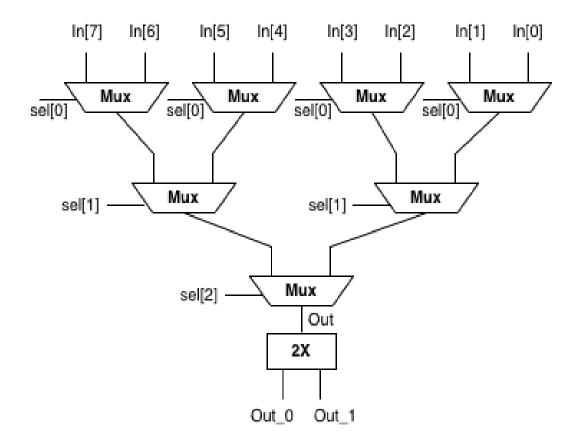

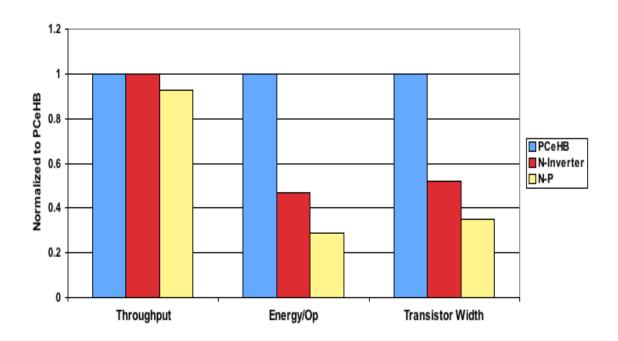

| 3.14 | 8-to-1 multiplexor with 2 copies of Output                           | 55 |

| 3.15 | 8-to-1 multiplexor design trade-offs for different pipeline styles . | 56 |

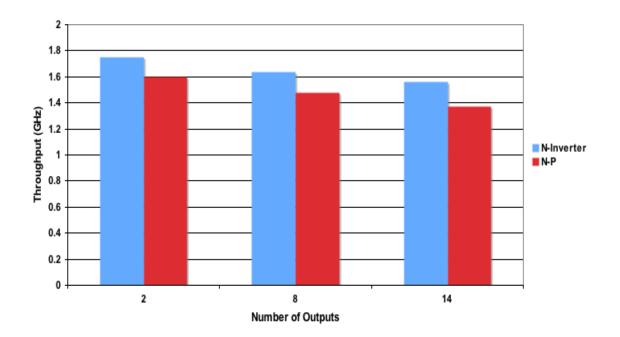

| 3.16 | Throughput dependency on the number of outputs                       | 57 |

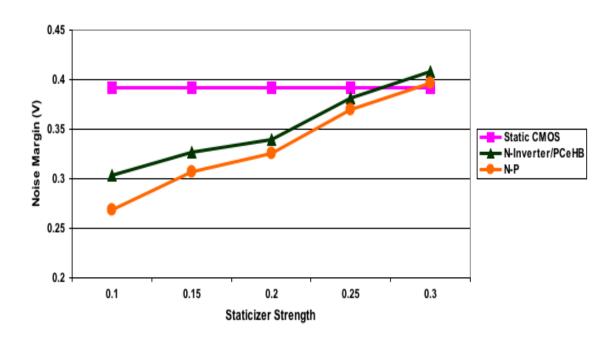

| 3.17 | Noise margin analysis                                                | 58 |

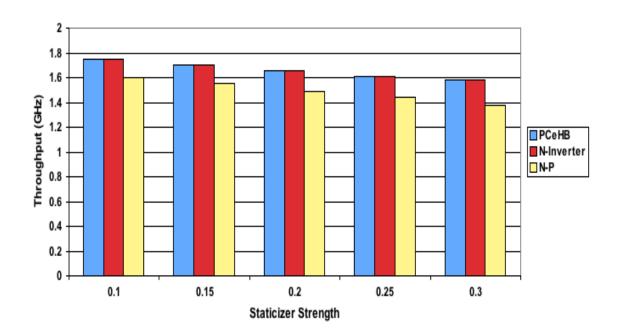

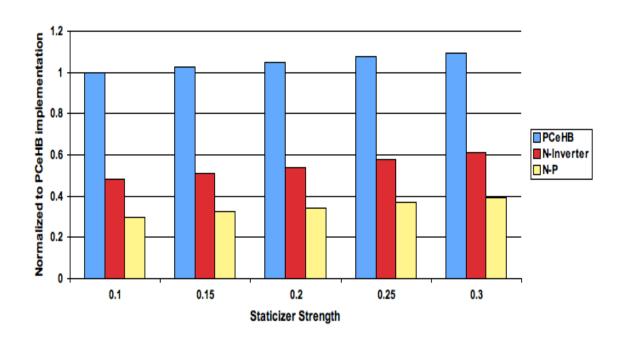

| 3.18 | Effect of staticizer strength on pipeline throughput                 | 59 |

| 3.19 | Effect of staticizer strength on energy/op                           | 60 |

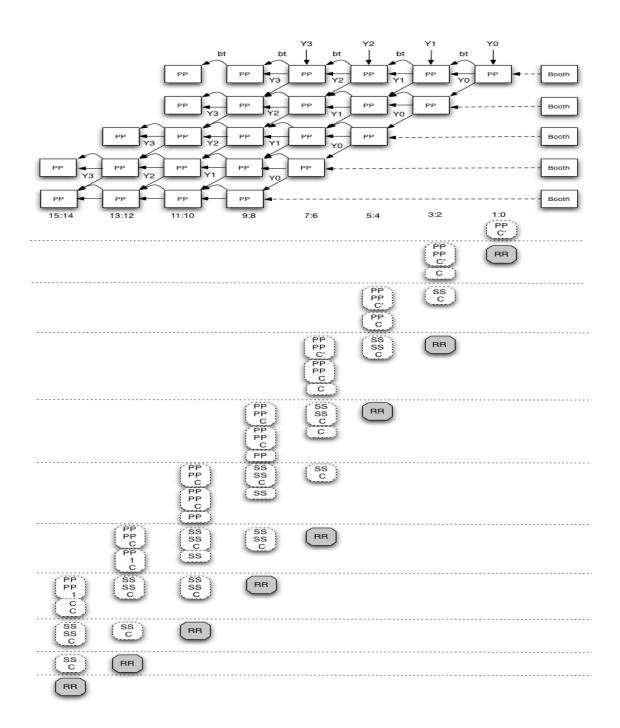

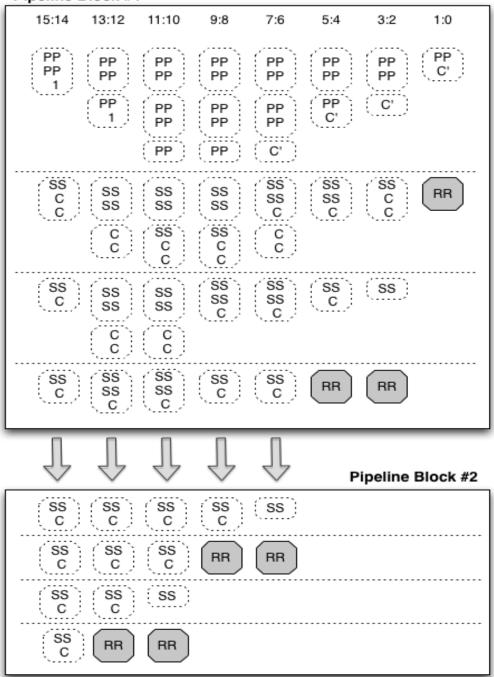

| 3.20 | 8x8-bit multiplier architecture using PCeHB pipelines                | 63 |

| 3.21 | 8x8-bit multiplier using N-P pipelines                               | 65 |

| 3.22<br>3.23 | Power consumption breakdown of N-P and N-Inverter pipelines<br>8x8-bit multiplier throughput vs energy for three different | 67  |

|--------------|----------------------------------------------------------------------------------------------------------------------------|-----|

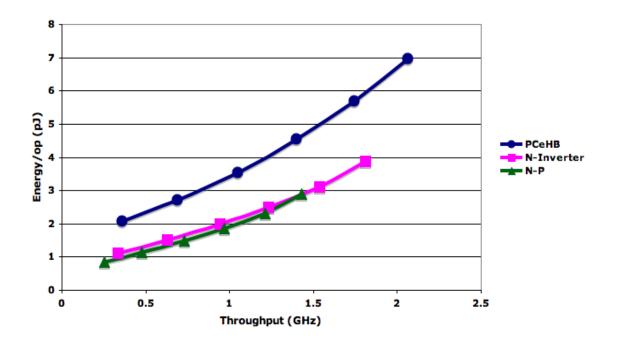

|              | pipeline styles                                                                                                            | 69  |

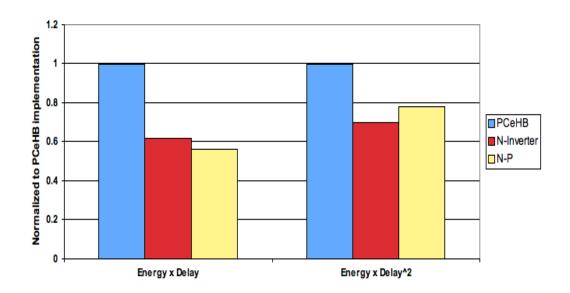

| 3.24         | 8x8-bit Multiplier energy-delay analysis for three different pipeline styles                                               | 70  |

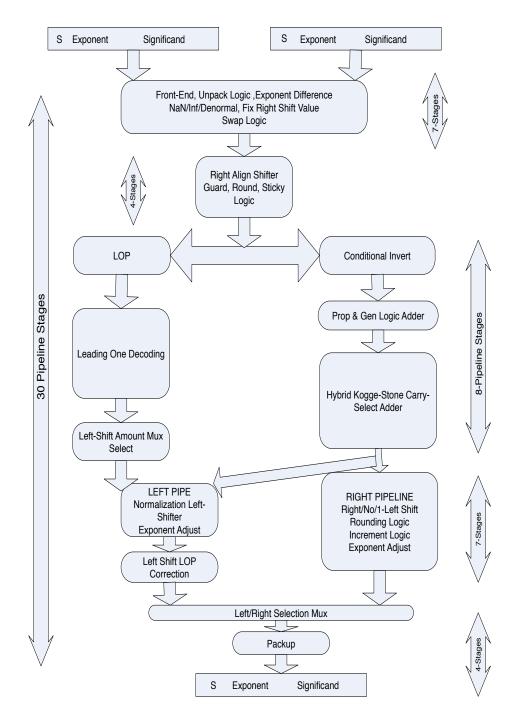

| 4.1          | Asynchronous Baseline FPA Architecture                                                                                     | 75  |

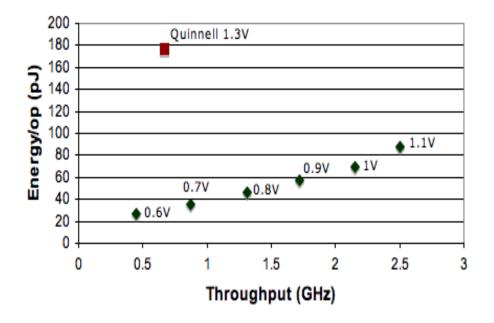

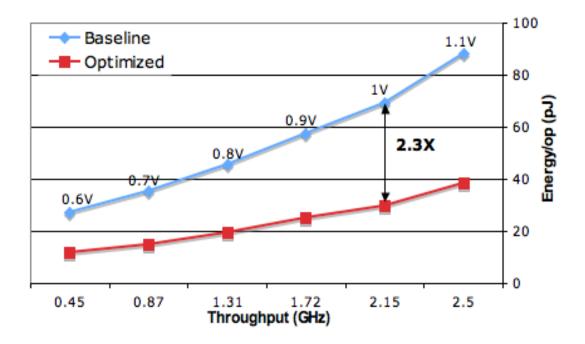

| 4.2          | Baseline FPA Energy vs Throughput                                                                                          | 79  |

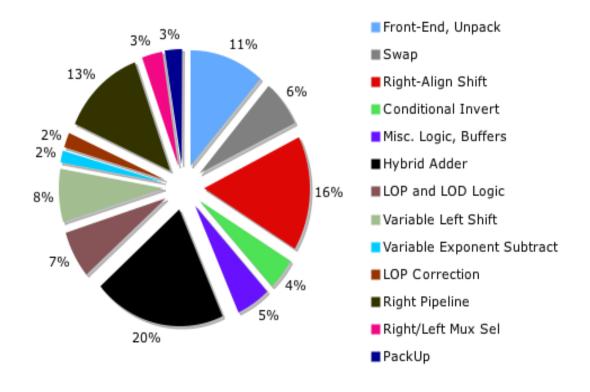

| 4.3          | FPA Pipeline Power Breakdown                                                                                               | 81  |

| 4.4          | Radix-4 Ripple-Adder Carry-Length                                                                                          | 82  |

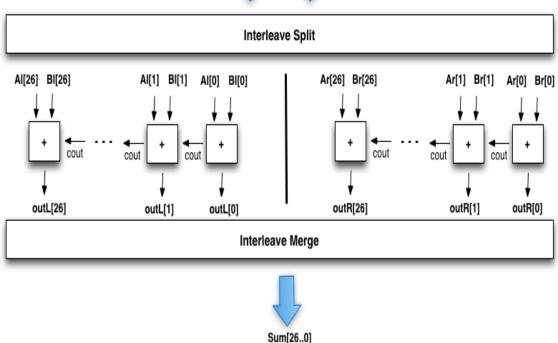

| 4.5          | Interleaved Asynchronous Adder                                                                                             | 83  |

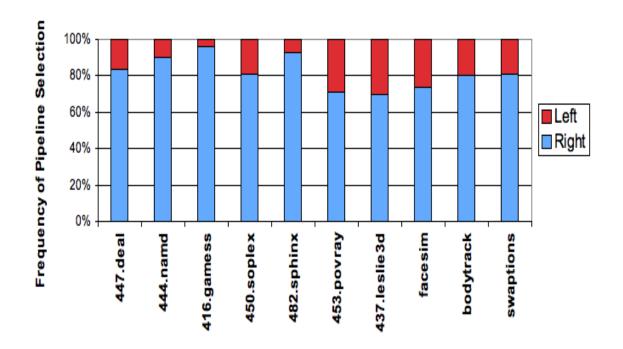

| 4.6          | Left/Right Pipeline Frequency                                                                                              | 87  |

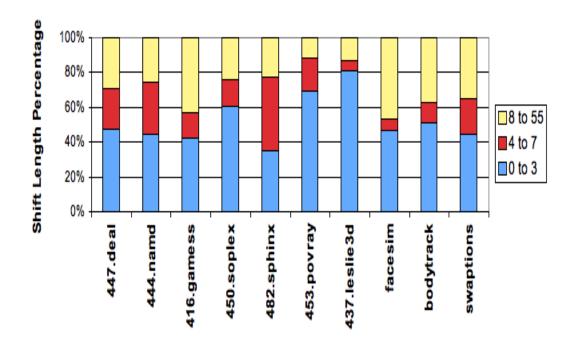

| 4.7          | Right Align Shifter Statistics                                                                                             | 89  |

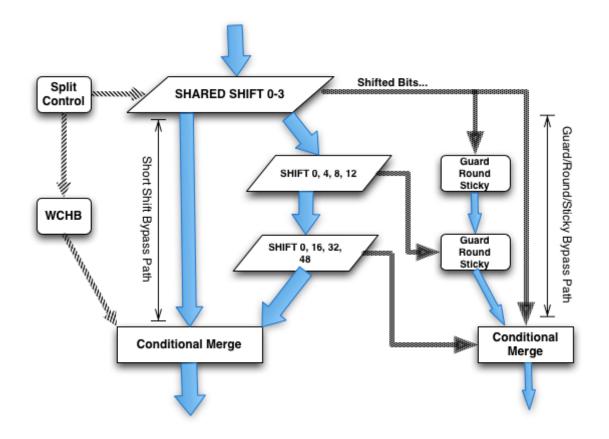

| 4.8          | Two-Path Right-Align Shift                                                                                                 | 90  |

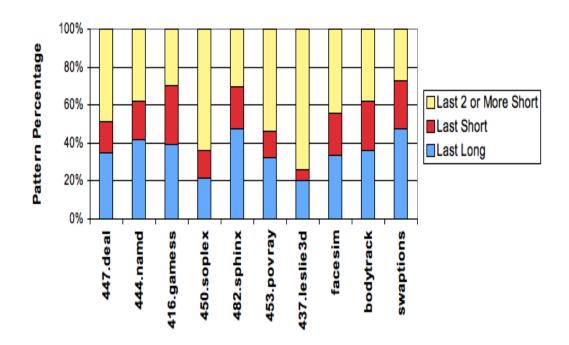

| 4.9          | Right Align Shift Short Path Pattern                                                                                       | 92  |

| 4.10         | Radix-4 Incrementer Carry Length                                                                                           | 95  |

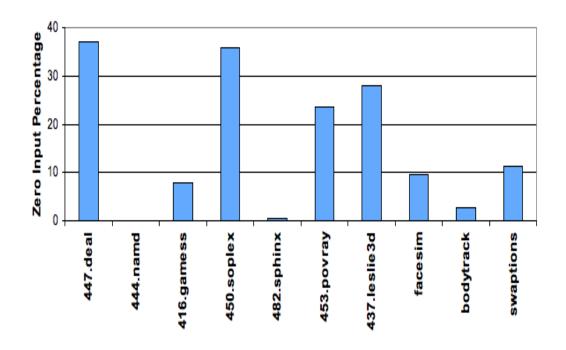

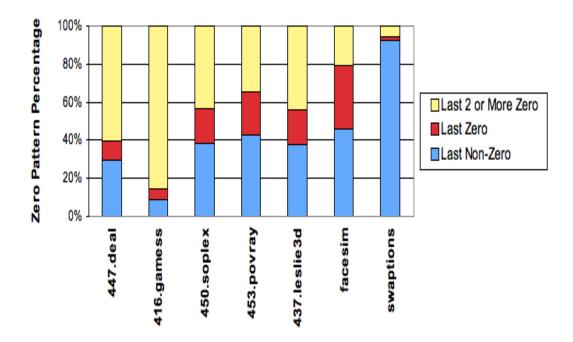

| 4.11         | Zero-input Operands                                                                                                        | 96  |

| 4.12         | Zero-input Pattern                                                                                                         | 97  |

| 4.13         | Zero-Path Control Slack Analysis                                                                                           | 98  |

| 4.14         | 2-WCHB Zero-Path Control Slack                                                                                             | 99  |

| 4.15         | Optimized vs. Baseline                                                                                                     | 102 |

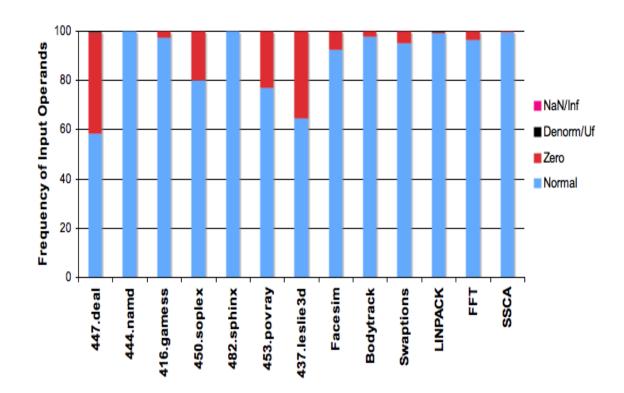

| 5.1          | Frequency of floating-point instructions                                                                                   | 108 |

| 5.2          | FPM Pipeline Power Breakdown                                                                                               | 109 |

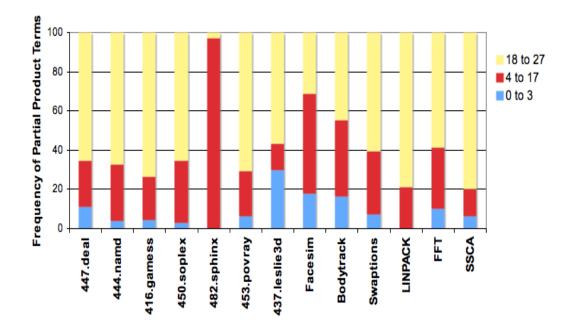

| 5.3          | Number of partial products terms with original Booth algorithm .                                                           | 113 |

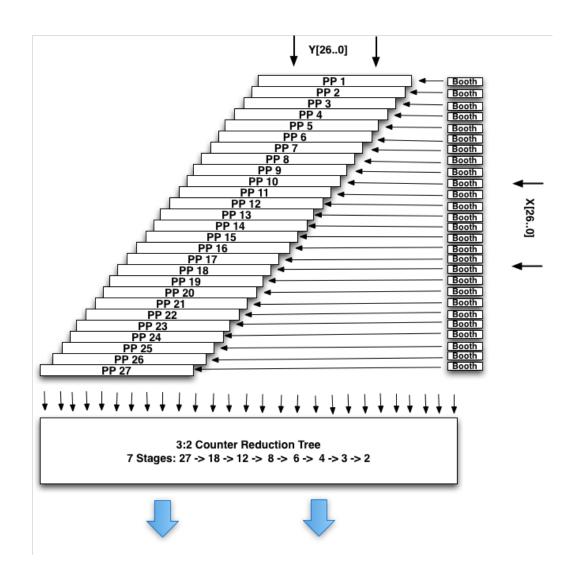

| 5.4          | Radix-4 modified Booth multiplier.                                                                                         | 115 |

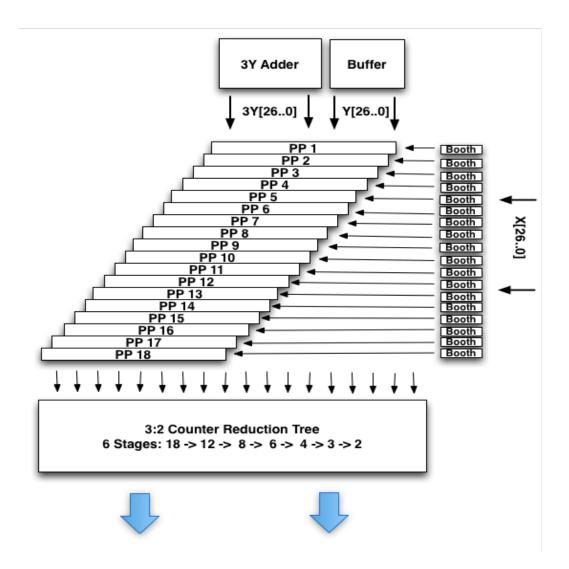

| 5.5          | Radix-8 modified Booth multiplier.                                                                                         | 116 |

| 5.6          | Radix-4 3Y Adder Longest Carry Length                                                                                      |     |

| 5.7          | Interleaved 3Y Adder                                                                                                       | 119 |

| 5.8          | Radix-8 Multiplier Array                                                                                                   | 122 |

| 5.9          | 8x4 Multiply Logic Block                                                                                                   | 123 |

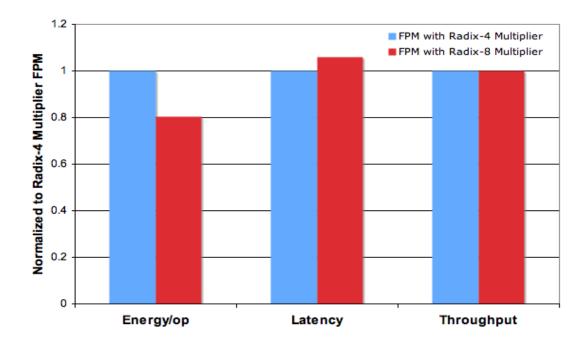

| 5.10         | Radix-4 Multiplier vs. Radix-8 Multiplier                                                                                  | 126 |

| 5.11         | Longest ripple-carry length for computing CPA carry input                                                                  | 128 |

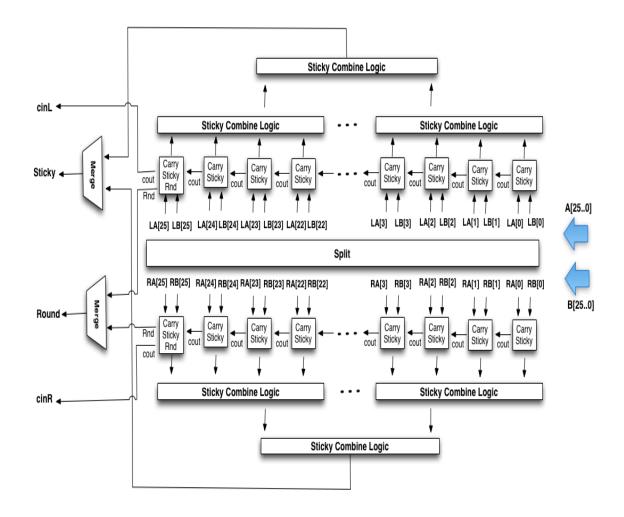

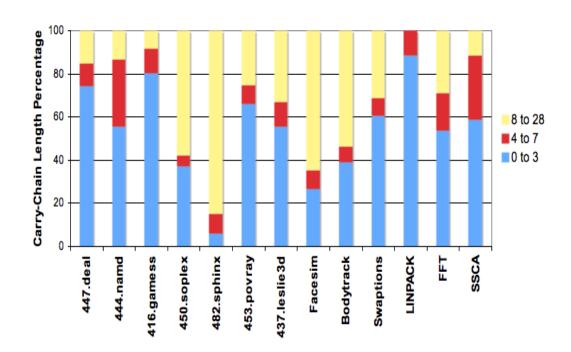

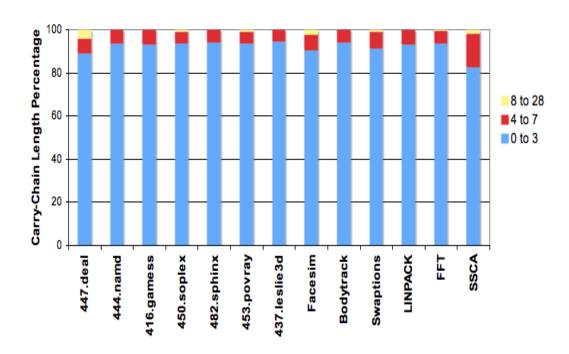

| 5.12         | Interleaved topology to compute sticky-bit and carry input                                                                 | 130 |

| 5.13         | Sticky-bit ripple-carry chain length                                                                                       | 131 |

| 5.14         | CPA ripple-carry chain length                                                                                              |     |

| 5.15         | Floating-point multiplier with support for special case inputs                                                             | 135 |

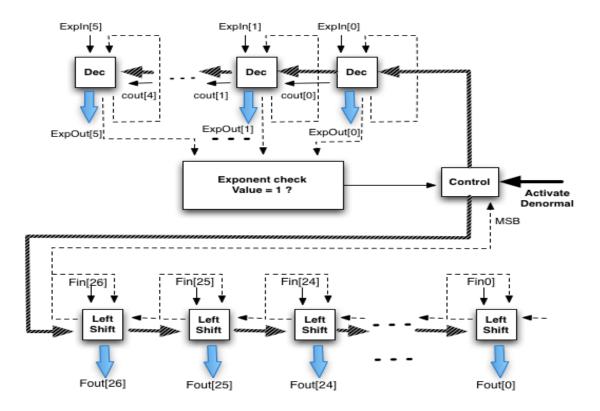

| 5.16         | Denormal operation hardware                                                                                                | 137 |

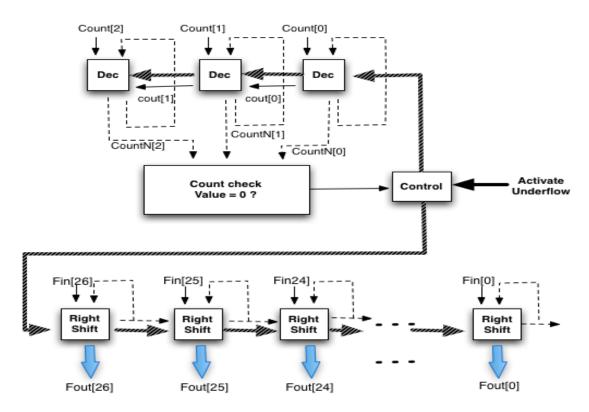

| 5.17         | Supporting underflow case in hardware                                                                                      | 139 |

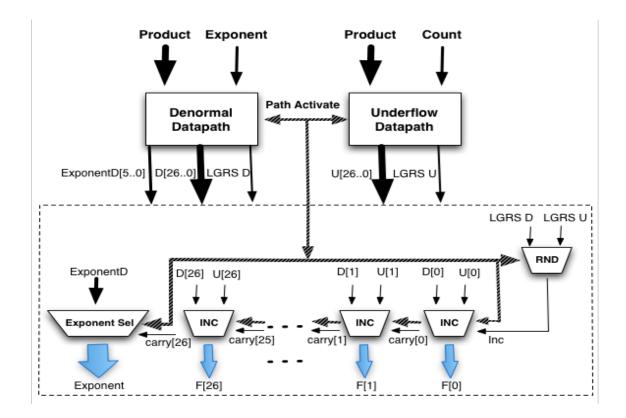

| 5.18         | Unified rounding hardware for denormal/underflow cases                                                                     | 141 |

| 5.19         | Operand profile of floating-point multiplication instructions                                                              |     |

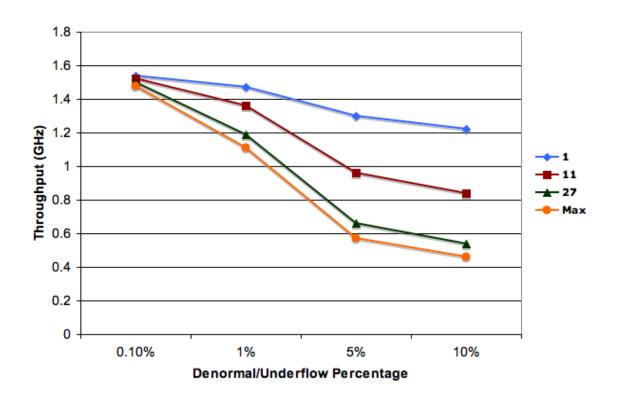

| 5.20         | FPM throughput with varying proportion of denormal/underflow                                                               |     |

|              | cases                                                                                                                      | 145 |

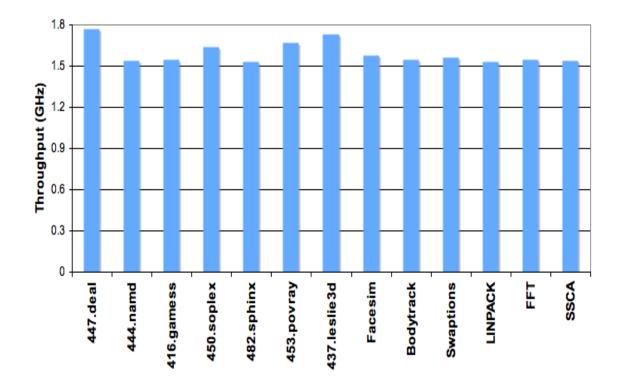

| 5.21         | FPM throughput across various floating-point applications                                                                  | 146 |

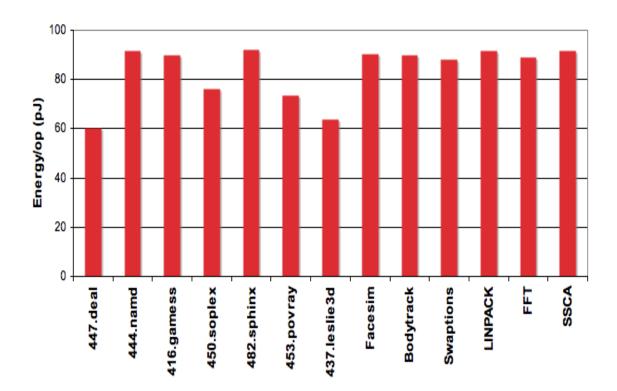

| 5.22 | FPM energy per operation across various floating-point applica- |   |

|------|-----------------------------------------------------------------|---|

|      | tions                                                           | 7 |

## **List of Abbreviations**

- CMOS Complementary Metal-Oxide Semiconductor

- CSA Carry Save Adder

- FPA Floating-Point Adder

- FPM Floating-Point Multiplier

- LOD Leading One Detection

- LOP Leading One Prediction

- NMOS n-diffusion Metal-Oxide Semiconductor

- PCeHB Pre-charge enable Half Buffer

- PMOS p-diffusion Metal-Oxide Semiconductor

- QDI Quasi-Delay Insensitive

- WCHB Weak Conditioned Half Buffer

- VDD Positive Power Supply Node

- VLSI Very Large Scale Integration

### Chapter 1

### Introduction

#### 1.1 Motivation

Efficient floating-point computation is important for a wide range of applications in science and engineering. Using computational techniques for conducting both theoretical and experimental research has become ubiquitous, and there is an insatiable demand for higher and higher performing VLSI systems. Despite the remarkable advances in computing in the last few decades, the computing needs of many emerging applications in the fields of molecular biology, quantum chemistry, weather detection patterns, fluid dynamics, speech recognition, and financial services are far from being fully satisfied. Some of these emerging applications are essentially needed to address many critical global challenges. These include climate change, curing life-threatening diseases, discovering sustainable and alternative sources of energy, and predicting natural calamities to name a very few. To meet the growing demands of some of these critical applications, today's faster super computers have exceeded the 1 *petaFLOP* (quadrillion floating-point operations per second) performance mark. Recently, Japan's K Computer [6] achieved a performance of 8.162 *petaFLOPS* to clinch the title of world's fastest supercomputer. But this performance came at the cost of 9.89 megawatts in power, which may be enough to power a small town. Furthermore, these power hungry systems require elaborate and expensive cooling systems to ensure proper operation. These results mean that the manufacturers of large, fast supercomputers and the VLSI chip designers of the underlying workhorse processors can no longer afford to design for performance only. Top 500 supercomputer ranking takes into account the energy-efficiency of the system as well as its performance.

Traditionally, VLSI designers primarily relied on CMOS technology and voltage scaling to reduce power consumption [11]. However, with the scaling of CMOS technology into ultra-deep sub-micron range, this no longer yields the desired power reduction. With the transistor threshold voltage fixed [28],  $V_{DD}$  has been scaling very slowly if at all, which means all performance improvements come at an increased energy consumption. Furthermore, process variations in deep sub-micron range have made devices far less robust, which is increasingly making it difficult for synchronous designers to overcome the problems associated with clock skew rates and clock distribution [18]. The findings of a recent in-depth study, to explore and devise ways to further scale supercomputer *petaFLOP* performance by 1000X, indicate the inadequacy of current design practices and technologies to achieve the desired throughput within a sustainable power budget [1]. This underscores a pressing need for alternate design practices, to reduce energy consumption for floating-point computations

while preserving robust behavior in advanced technology nodes, which is the core motivation behind this thesis.

At the other end of the spectrum, embedded systems that have traditionally been considered low performance are demanding higher and higher throughput for the same power budget to support compute-intensive floating-point applications that improve the user experience. Some of these applications include, but are not limited to, advanced gaming and animation softwares based on complex physics motion equations, voice recognition, facial simulation, graphics rending, advanced image and video processing applications. Since these applications have to be deployed on portable devices with limited battery-life, it is critical that we develop *energy-efficient* floating-point hardware for these embedded systems, not simply high performance floating-point hardware.

#### **1.2** Operand Dependent Floating-Point Unit Design

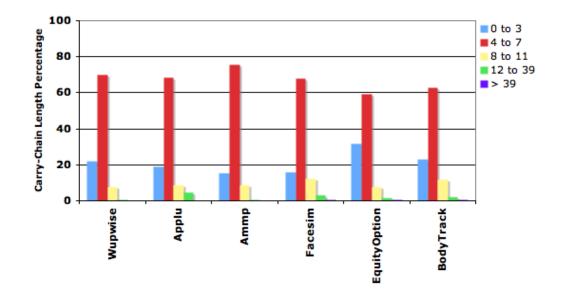

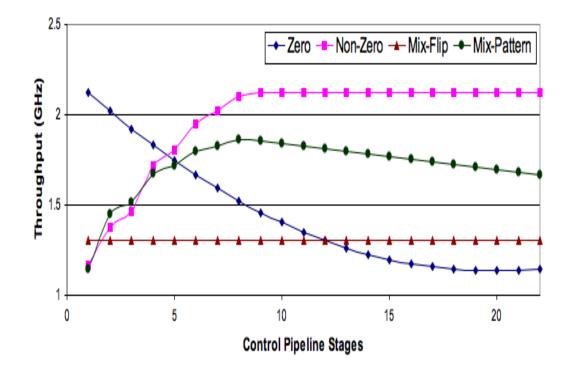

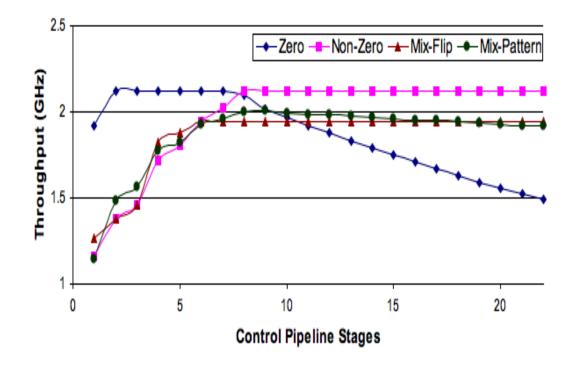

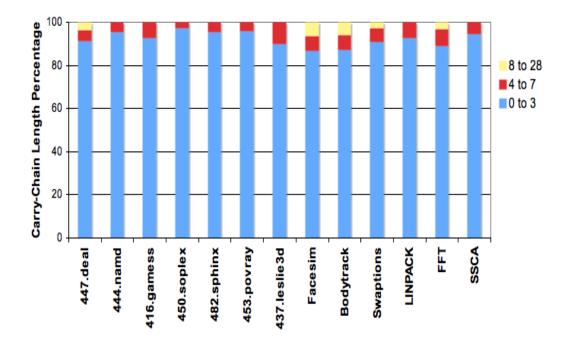

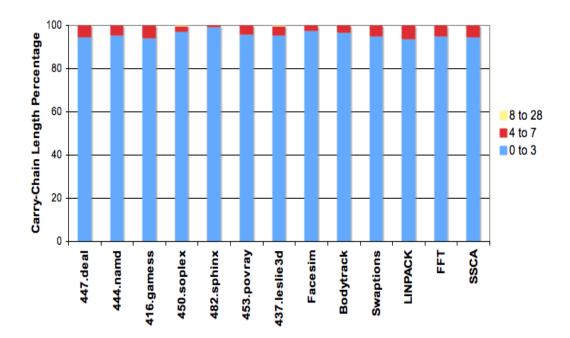

Synchronous floating-point units, limited by worst-case computation delay, include complex circuitry to attain constant latency and throughput for the best, average, and worst case input patterns alike. Consider an N-bit adder circuit, for example. The delay of this adder depends on how fast carry reaches each bit position. In the worst case, the carry has to be propagated through all bits, which causes synchronous designers to consider complex, power-hungry adder designs to meet their stringent timing requirements. The biggest disadvantage of this design methodology is that it results in the same power consumption for the best case carry propagation of zero bit position, even though the best case could have been done much faster and more energy efficiently using much simpler circuits. A preliminary input profile of a number of floating-point applications from SPEC [5] and PARSEC [9] benchmarks, shown in Figure 1.1, indicates that the worst case of carry propagation happens very rarely, if at all, in a 56-bit adder unit typically found in double-precision floating-point adder design.

Figure 1.1: Longest carry-chain length in a 56-bit Adder

The observation that there are infrequently occuring cases that make the hardware difficult/slow leads to the natural question: can we design an energy-efficient *asynchronous* floating-point unit? An asynchronous circuit does not use a clock signal, and is not constrained to a global timing constraint. Perhaps we could design an IEEE-compliant floating-point unit that was a bit slower when certain infrequent cases occurred. This could result in a significant energy reduction during normal operation. Self-timing would enable this flexibility at a very fine grain, allowing for operand-dependent performance and energy consumption. In this thesis, we explore the possibilities of data dependent optimizations in floating-point arithmetic circuits.

#### 1.3 Asynchronous Circuit Design

Asynchronous quasi-delay-insensitive (QDI) circuits, with their robustness to process variations, no global clock dependence, and inherent perfect clock gating, represent a highly feasible design alternative for future chip design. QDI circuits are also robust to voltage and delay variations, hence easing some of the design verification efforts. QDI circuits have been used in numerous highperformance, energy-efficient asynchronous designs [63] [23], including a fullyimplemented and fabricated asynchronous microprocessor [42]. In this thesis, we harness the operand dependent execution and timing flexibility of asynchronous pipelined circuits to design and implement high-performance, energy efficient, asynchronous floating-point arithmetic circuits with truly data dependent performance and energy footprint.

QDI circuit templates, though robust, lose some of their energy efficiency gains in implementing handshakes between different parallel pipeline processes. To ensure QDI behavior for each handshake, every up and down transition within a pipeline is sensed, which leads to significant handshake circuitry and energy overhead. High throughput QDI pipelines only include a small amount of logic in each stage. The large number of pipeline stages required for high throughput make the handshake overhead a significant proportion of the total power consumption. In this thesis, we try to circumvent the problem of high handshake overhead in commonly used QDI pipelined circuits but without sacrificing robustness.

#### 1.4 Thesis Contribution and Organization

The primary contributions of this thesis are listed as follows:

- Design of two novel pipeline templates, which greatly minimize the handshake circuitry of commonly used QDI templates by taking advantage of some easily satisfiable timing assumptions. Compared to QDI templates, the average throughput and latency are preserved, while the transistor area is greatly minimized. As it is in the case of QDI templates, the correctness of these proposed templates is not a function of input and output arrival times, which makes them very robust. We also present detailed design trade-off analysis of these templates to help future designers make appropriate pipeline selection based on their design constraints.

- Profiling results of various real life floating-point applications from many diverse fields. The bit-level input and computation patterns within several key logic blocks in the floating point unit datapath make a strong case for introducing operand-based optimizations for energy efficiency.

- The design and implementation of a first high-performance, energyefficient, double-precision, asynchronous floating-point adder (FPA). The FPA is implemented using asynchronous QDI pipelines and is fully IEEE-754 standard compliant. It employs a number of novel operanddependent optimization techniques to greatly reduce the circuit complexity and power consumption of various key logic blocks within the FPA datapath, while preserving average throughput and latency.

- A full-transistor level implementation of an asynchronous floating-point multiplier (FPM) datapath is presented. To our knowledge, our FPM is

a first high-performance, double-precision, asynchronous unit of its kind. It uses a mix of QDI and the newly proposed pipeline templates to improve energy efficiency of various key logic blocks within the datapath. A higher radix array multiplier design is introduced. The FPM provides full hardware support for difficult to implement special cases in the IEEE-754 standard with minimal complexity.

The rest of the thesis is organized as follows: In Chapter 2, we provide a background on IEEE-754 floating-point standard and several synchronous floating-point unit designs from academia and industry. It provides details of various floating-point applications that were profiled and outlines the key operations within the FPA and FPM datapaths. An introduction to asynchronous QDI pipelines is also presented. Chapter 3 introduces our novel energy-efficient pipeline templates. It provides a detail discussion on various design trade-offs of these templates and evaluates their efficacy using a non-trivial implementation of an 8x8 Booth-encoded array multiplier design. In Chapter 4, we present the design and implementation of our high-throughput, energy-efficient FPA unit. The application profiling results for floating-point addition operations are presented. All operand-dependend optimizations are discussed in detail. We conclude the chapter with an in-depth evaluation of our FPA across various input sets. Chapter 5 presents our FPM datapath design. It introduces a higher radix array multiplier which utilizes input patterns to significantly reduce overall circuit complexity and energy consumption while preserving the average throughput. Hardware implementation of special cases within the IEEE standard is also discussed. In Chapter 6, we summarize our key findings and their usefulness to future research.

### Chapter 2

### Background

In this chapter, we provide a background on floating-point computations, their various hardware implementations, and a set of diverse floating-point application benchmarks that we used for data dependent optimizations. The chapter also includes a brief introduction to asynchronous quasi-delay-insensitive (QDI) pipelines.

#### 2.1 Floating-Point Computations

Today, most floating-point is IEEE-compliant or has an IEEE-compliant mode. A thorough background knowledge on what the standard entails is very important to understand the various trade-offs involved in floating-point hardware design.

#### 2.1.1 IEEE Floating-Point Standard

The IEEE 754 standard [49] for binary floating-point arithmetic provides a precise specification of floating-point number formats, computation operations, and exceptions and their handling. This specification was determined after much debate, and it took several years before hardware vendors developed IEEE-compliant hardware. Part of the challenge was the belief that: (i) implementing most of the standard was sufficient; (ii) ignoring a few infrequently occuring cases led to more efficient hardware (e.g. [33]). Unfortunately ignoring certain aspects of the standard can lead to unexpected consequences in the context of numerical algorithms. Today, most floating-point hardware is IEEEcompliant or has an IEEE-compliant mode.

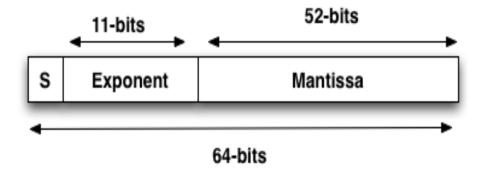

The IEEE format specifies two main groups of floating-point format: *single-precision* and *double-precision*. In this thesis, we primarily focus on double-precision format since it is commonly used in most scientific and emerging applications. Figure 2.1 depicts the 64-bit double-precision floating-point number format. It comprises 1-bit of sign, 11-bits of exponent, and 52-bits of mantissa (also known as the significand).

The value of a normalized number, *X*, being represented is as follows:

$X = (-1)^{S} * 1.M * 2^{(E-bias)}$

where *S* is the value of the sign bit, *M* corresponds to the mantissa bits, *E* corresponds to the exponent bits, and *bias* has a value of 1023 in double-precision floating-point format. The standard also specifies the format of a *denormal* number to represent the result of the computation whose value is between the smallest possible representation of a normalized number and zero. The value of a

Figure 2.1: Double precision floating-point format

denormal number, *X*, being represented is as follows:

$$X = (-1)^{S} * 0.M * 2^{(1-bias)}$$

and differs from a normal number in that there is no implied bit and the exponent with a value of zero is forced up by 1 to *Emin*, which is equal to -1022 in double-precision format. The format specifies other special types such as Not-a-Number (*NaN*), + $\infty$ , and - $\infty$ . These special cases are detected by checking the exponent and mantissa bits. For *NaN*, all exponent bits are one and the mantissa is non-zero. Similarly,  $\infty$  is indicated by an exponent comprising one in each bit position but with zero mantissa. A denormal number is indicated by a zero exponent and mantissa bits are zero. The IEEE format also includes four different rounding modes, which specify how to deal with inexact floating-point outputs.

The combination of a vast range of inputs, special cases, and rounding modes makes the hardware implementation of fully IEEE 754 standard compliant floating-point arithmetic a very challenging task.

#### 2.1.2 Floating-Point Adder

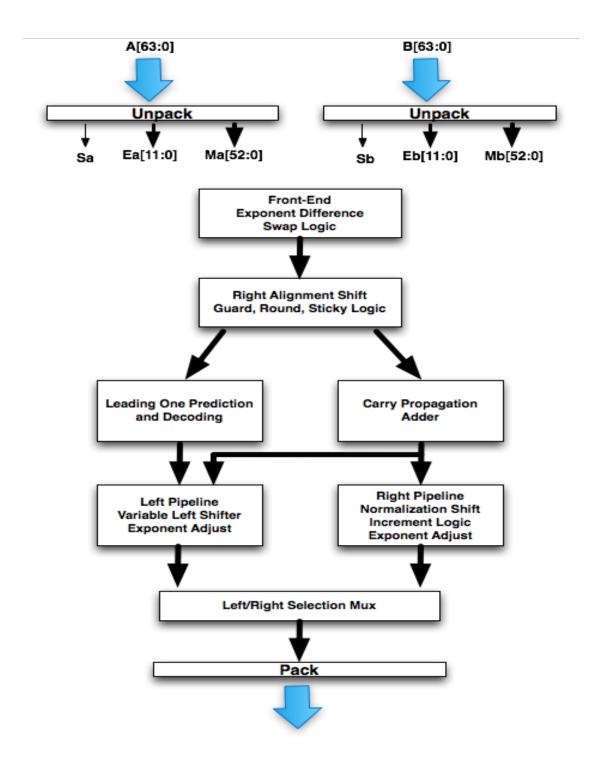

A floating-point adder is used for the two most frequent floating-point operations: addition and subtraction. It requires much more circuitry to compute the correctly normalized and rounded sum compared to a simple integer adder. All the additional circuitry makes the FPA a complex, power-consuming structure. Figure 2.2 shows the FPA datapath for two double-precision 64-bit inputs.

The following summarizes the key operations required to implement an IEEE-compliant FPA:

- The first step in the FPA datapath is to unpack the IEEE representation and analyze the sign, exponent, and significands bits of each input to determine if the inputs are standard normalized or are of one of the special types (NaN, Infinity, Denormal).

- Prior to actual addition or subtraction, the absolute difference of the two exponents is used as the shift amount for a variable right shifter which aligns the smaller of the operands.

- In parallel with the right align shifter, the guard, round, and sticky bits are computed to be used for rounding in latter stages of the FPA datapath.

- The next step is the addition or subtraction of two significands based on sign information.

- Most high-performance FPAs use a special-purpose circuit popularly known as a Leading-One-Predictor and Decoder (LOP/LOD) to predict the position of the leading one in parallel with the addition/subtraction step.

Figure 2.2: Floating-point Adder Datapath

- The post addition steps include normalizing the significands. This may require either a left shift by a variable amount (using the predicted value from LOP), no shift (if the output is already normalized), or a right shift by one bit (in case of carry-out when the addition inputs have the same sign).

- The exponent is adjusted based on the shift amount during normalization. In parallel, the guard, round, and sticky bits are updated and are used, along with the rounding mode, to compute if any rounding is necessary. The sign of the sum is also computed.

- In case of rounding, the exponent and significand bits are updated appropriately.

- The final stage checks for a NaN, Infinity, or a Denormal outcome before producing the correct result.

The complexity of the FPA datapath is not dominated by any single large logic block, but instead it is distributed across multiple logic blocks. This necessitates the need to optimize all blocks to gain significant improvements in energy efficiency.

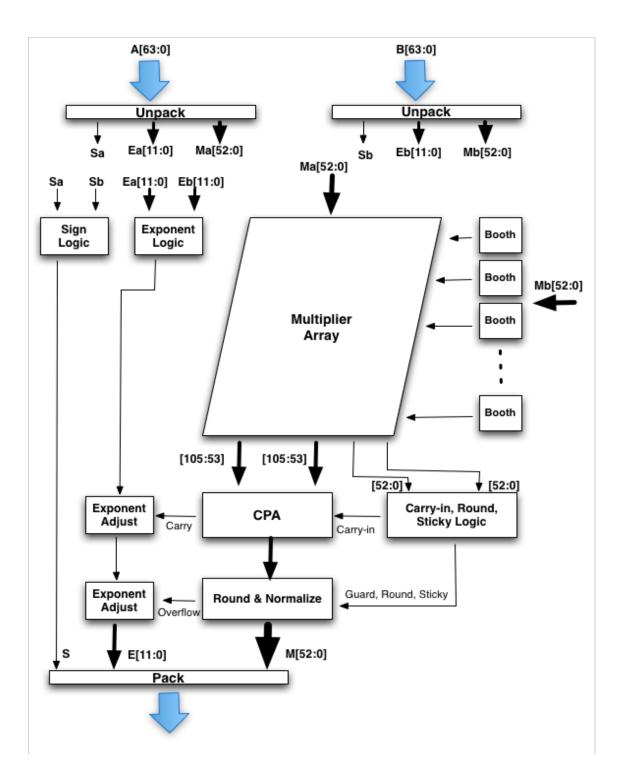

#### 2.1.3 Floating-Point Multiplier

In terms of micro-architectural complexity, for operations involving normal inputs, the floating-point multiplier (FPM) datapath is relatively simpler than the FPA datapath. It does not require logic blocks such as *Right Alignment Shifter, Leading One Detection and Prediction unit,* and *Variable Length Normalization Shifter,* which increase the complexity of FPA datapath. The denormal and underflow operations in the FPM may require variable length shift for normalization. We discuss these operations and their hardware requirements later in a separate section. The FPM datapath for double precision multiplication operation is shown in Figure 2.3.

The following summarizes the key steps in an FPM datapath:

- The first step in the FPM datapath is to unpack the IEEE representation and analyze the sign, exponent, and mantissa bits of each input to determine if the inputs are standard normalized or are of one of the special types (NaN, infinity, denormal).

- The mantissa bits are extended with the implicit bit. It is set to one for normal inputs and zero for a denormal input.

- The 53-bit long mantissas of both inputs are used to generate partial products corresponding to a 106-bit product. Since high throughput and low latency are of essence in floating-point applications, most FPMs use some form of an array multiplier, such as a booth-encoded multiplier as shown Figure 2.3, to meet the performance demands. Most array multipliers employ an array of carry-save-adders (CSAs) [71] to reduce the large number of partial products to two final full product-length bit streams.

- The most significant 53-bits of the two output bit streams from the CSA array are summed up using a carry propagation adder (CPA) to generate a 53-bit mantissa. The least significant 53-bits are used to generate the carry input to the CPA as well as compute the guard, round, and sticky bits to be used in post normalization rounding.

- In parallel, the exponent logic computes the resulting exponent, which is a sum of the exponent values of both inputs minus the bias. The bias has

Figure 2.3: Floating-point Multiplier Datapath

a value of *1023* in case of double-precision operations. The sign of final product is also computed.

- The post multiplication step includes normalization of the 53-bit mantissa. For normal inputs and non-underflow cases, either the mantissa is already normalized or it may require a right shift by a single bit position, in which scenario the exponent is adjusted, in parallel, by adding one to it. The guard, round, and sticky bits are updated and are used, along with the round mode, to determine if the product needs to be rounded or not.

- In case of rounding, the mantissa is incremented by one. If rounding yields a carry out, the exponent is adjusted by adding one to it and right shifting the mantissa by one bit position.

- The final stage checks for a NaN, infinity, or a denormal outcome before outputting the correct result in the IEEE format.

With normalization step limited to a simple shift of no more than one-bit position and the exponent logic comprising only 11-bit long arithmetic, the FPM's complexity is largely a function of its 53x53 multiplier, sticky bit computation block, and the final carry propagation adder. In this thesis, we present various structural and circuit-level optimization techniques to reduce the complexity and power consumption footprint of the aforesaid logic blocks.

#### 2.2 Floating-Point Application Benchmarks

The high complexity of synchronous floating-point hardware arises out of the need to compute the worst case floating-point operation within a stringent timing margin. The important question to ask is how often the worst-case happens. If it happens very frequently then it justifies burning extra power with complex circuits to boost overall performance.

To answer this question, we used Intel's PIN [38] toolkit to profile input operands in a few floating-point intensive applications. This profiling analysis gave us a great insight into the average case input properties in various real life applications. We exploit this knowledge to provide a number of operand dependent optimizations, which enable us to use simple asynchronous circuits to meet our performance targets at a much reduced energy consumption.

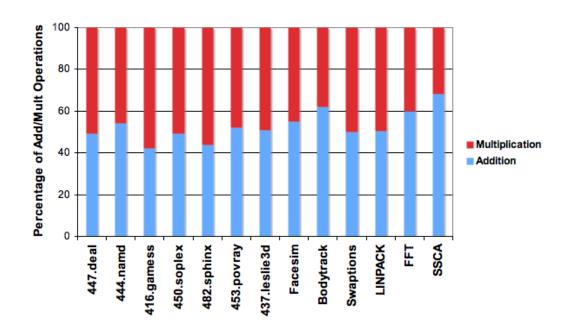

For the floating-point adder (FPA) design, we profiled the followed application benchmarks from SPEC2006 [5] and PARSEC [9] benchmark suites using reference input sets:

- 447.*deal*: This C++ program utilizes a specialized program library targeted at adaptive finite elements and error estimation. It has application in the fields of fluid flow, electro-magnetics, acoustics, and general relativity to name a few.

- 444.*namd*: It simulates large bio-molecular systems. Most of the runtime is spent calculating inter-atomic interactions in a small set of functions.

- 416.gamess: It implements a wide range of quantum chemical computations.

- *450.soplex*: It solves a linear program using the simplex algorithm. Like most other implementations of the simplex algorithm, it employs algorithms for sparse linear algebra.

- *482.sphinx*: This is a widely-known speech recognition system from Carnegie Mellon University.

- *453.povray*: It is an image rendering, ray-tracer program. Intersections of rays with geometry objects are computed by solving complex mathematical equations using numerical methods or directly.

- *437.leslie3d*: It is a computational fluid dynamics solver used to investigate turbulence phenomena such as mixing, combustion, and acoustics.

- *facesim*: It simulates the motions of human face using underlying physics motion equations.

- *bodytrack*: A computer vision application which tracks the human body with multiple cameras. It has applications in video surveillance and character animation fields.

- *swaptions*: A financial application which uses Monte Carlo simulation to price a portfolio of swaptions.

For the floating-point multiplier (FPM) design, we profiled three more applications listed below:

- *FFT*: It measures the floating-point rate of execution of double-precision complex three-dimensional Discrete Fourier Transform [2].

- *LINPACK*: It is a collection of subroutines that analyze and solve linear equations and linear least-squares problems [4]. These subroutines are commonly used to characterize the performance of highest performing supercomputers.

- *SSCA*: A graph theory benchmark representative of computations in informatics and national security [3].

Although, all these applications come from very diverse fields, the underlying computations have their roots in similar mathematical and physics principles. Our goal is to exploit the existing common input patterns in all these benchmark applications to improve energy efficiency and reduce floating-point unit's circuit complexity. The input operands in actual benchmark runs were saved to disk, and then used for statistical analysis. The application profiling statistics in the following chapters were tabulated using ten billion input operands for each application.

#### 2.3 Related Work

#### 2.3.1 Asynchronous Arithmetic

The use of asynchrony to improve the performance of arithmetic circuits has been exploited by a number of different researchers. As early as 1946, von Neumann proposed using an asynchronous integer adder because the average-case delay for a ripple-carry adder is  $O(\log N)$  where N is the number of bits in the input assuming that the input bits are independent, identically distributed (i.i.d.) random variables [13]. More recently it was shown that it is possible to design an asynchronous integer adder with an average-case latency of  $O(\log \log N)$  for i.i.d. inputs [40] and that the design achieves the optimal asymptotic averagecase latency for any input distribution [39]. There have been numerous papers on asynchronous adders with a variety of topologies (e.g. [42, 31, 25, 46]).

In terms of the multiplier design, the delay variability nature of iterative multipliers makes them a popular choice amongst asynchronous designers [19, 30]. An iterative multiplier utilizes a few functional units repeatedly to produce the result. In a simple iterative *n* by *n* multiplier implementation, where *n* is the number of bits, the product is computed after *n* iterations. Each iteration comprises a minimum n-bit addition and a serial shift by one-bit position. Furber et al [37] proposed a low power integer multiplier which exploits the commonly occurring pattern of low number of significant bits in integer inputs as means to reduce the total number of iterations. These iterative multiplier designs, though highly energy efficient and compact in terms of area, are not feasible to be used in a floating-point multiplier hardware due to their very high latency and low throughput and the fact that unlike the inputs in integer arithmetic, the most significant bits of floating-point mantissa inputs are non zero.

To our knowledge, the work of Joel Noche et al. [45] is the only published work on floating-point unit design using asynchronous circuits. Their work claims a full working single-precision floating-point unit (FPU). However, their FPU is completely non-pipelined, doesn't include any energy optimization techniques, and does not implement rounding logic. Their FPU has many orders of magnitude higher latency compared to all recent floating-point designs from synchronous domain. Their test vector for a floating-point addition operation included one addition of two arbitrary single-precision floating-point inputs for which they claim a completion time (latency) of 79 nanoseconds in a  $0.35\mu$ m process at 3.3V. For floating-point multiplication, they report a latency of 465 nanoseconds.

#### 2.3.2 Synchronous Floating-Point Adders and Multipliers

There is a large body of work on synchronous FPA and FPM design. Ercegovac and Lang [21] contains an overview of the different techniques used to optimize floating-point addition and multiplication.

Most of the earlier work on the FPA design has focused on improving FPA latency [61, 7, 48, 47]. Oberman [47] proposes the use of two align shifters to improve the latency of their single-precision FPA with only one rounding mode. Seidel and Even [61] propose a two-path FPA design to reduce overall latency. The R-path in their design deals with cases of effective addition (or subtraction with exponent difference greater than 1) and N-path deals with effective subtraction with exponent difference less than or equal to 1. Both paths are in operation at the same time and use their own significand adders.

There is less work on low-power FPAs compared to low-latency FPA design. Pillai et al. [52] propose the partitioning of the floating-point datapath into three distinct, clock-gated datapaths for activity reduction. Only one of the three paths is active during any operational cycle in their FPA. In our proposed transistor-level optimized asynchronous FPA, we also use controlinhibited pipelines but instead of using clock-gating to turn off the pipelines (which may worsen clock skew especially for high performance FPAs in deep submicron technologies) we use local asynchronous conditional split pipelines which have no effect on overall throughput. Also, our design goes beyond pipeline inhibitions as explained in sections 2.2 and 4.3. The FPA design by Quinnell et al. [54] is one of the rare fully-implemented designs (65nm SOI) from academia. Although, they use standard-cell library as opposed to our custom transistor-level construction, their work provides us with a good baseline to analyze our throughput and power results.

For synchronous FPM designs, the focus of prior work has been the array multiplier block, which is the single largest logic structure within the FPM datapath. Earlier designs have employed various architecture and circuit-level optimizations to reduce array multiplier latency and increase its throughput [73, 57, 48, 50]. However, there is relatively much less work on improving the energy efficiency of multiplier datapath [15], which is one of the primary contributions of this thesis. Traditionally, technology and voltage scaling has been deemed sufficient to provide the necessary reductions in energy consumption every few years. This is no longer the case any more. In this thesis, we propose a number of data dependent optimizations, both at the architectural and circuit-level, to significantly improve the energy efficiency of our FPM datapath.

Recent years have seen a number of contributions in the design of Fused-Multiply-Add (FMA) units [69, 54, 35, 60]. In [35], the authors propose techniques to reduce the latency of a floating-point addition operation in an FMA. In terms of performance and power-efficiency, the P6 Binary Floating-Point Unit [69] represents the state-of-the-art. It supports an extremely aggressive cycle time of 13FO4s. Power saving is done by clock-gating pipeline stages not in use. Power simulations at 1.1V, 4GHz, and 100% utilization in a 65nm SOI process consumed 310*m*W.

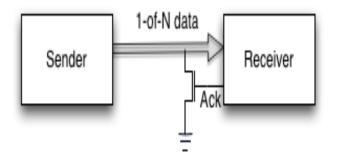

### 2.4 Asynchronous Pipelines

High performance asynchronous circuits are composed of many parallel processes. As opposed to synchronous circuits, which use a global clock to synchronize data tokens between different pipeline stages, these asynchronous parallel processes use handshake protocols to communicate with each other. These parallel processes are often referred to as fine-grain pipelined circuits. The finegrain pipelined circuits use designated channels for communication between processes. A channel comprises a bundle of wires and a communication protocol to transmit data from a sender to a receiver. There are numerous asynchronous fine-grain pipeline implementations [36] [72] [64] [24]. A robust family of these circuit templates is referred to as quasi-delay-insensitive (QDI) circuits.

## 2.4.1 Quasi-Delay-Insensitive Circuits

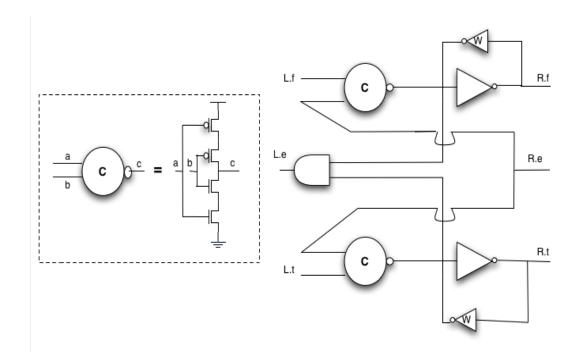

QDI circuit templates use 1-of-N encoded channels to communicate between different parallel processes. In an 1-of-N channel, a total of N wires is used to encode data with only one wire asserted at a time. Most high throughput QDI circuits either use 1-of-2 (dual-rail) or 1-of-4 encodings. In an 1-of-4 encoded channel communication as shown in Figure 2.4, *validity* is signified by setting one of the four data rails and *neutrality* is indicated by resetting of all four data rails. In a four phase handshake process, which is commonly used in most high speed QDI circuits, the sender process initiates the communication by sending data over the rails i.e. by asserting one of the data rails. The receiver process detects the presence of data and sends an acknowledge once it no longer needs the data. At this point, the sender process resets all its data rails. The receiver

process detects the neutrality of input tokens. It de-asserts the acknowledge signal once it is ready to receive a new data token. The cycle repeats.

Figure 2.4: Asynchronous pipelines: sender-receiver handshake protocol.

#### Weak-Condition Half-Buffer

The weak-conditioned half-buffer (WCHB) template is an energy efficient QDI pipeline template. Figure 2.5 shows a dual-rail WCHB pipeline along with a transistor-level depiction of a two input C-element gate which is used in a WCHB template. It is a simple buffer with dual-rail input token *L* and dual-rail output token *R*. The signal *L.e* is the inverted sense of the acknowledge signal seen in Figure 2.4.

A WCHB pipeline satisfies the *weak conditions* [62] i.e. the output being valid implies that the input is valid (checked by the NMOS logic stack of C-element), and the output being neutral implies that the input is neutral (checked by the PMOS logic stack of C-element). For logic computations requiring more than 2 inputs, a WCHB template requires too many stacked PMOS transistors, which makes it slower, more susceptible to noise, and less energy efficient. Therefore,

Figure 2.5: A WCHB pipeline stage

use of WCHB templates is usually limited to simple buffers and copy operations.

#### Pre-Charge enable Half-Buffer

The pre-charge enable half-buffer (PCeHB) [22] template, which is a slightly modified version of pre-charge half-buffer (PCHB) template proposed in [36] [72], is a workhorse for most high throughput QDI circuits. It is both small and fast with a cycle time of 18 transitions. In a PCeHB pipeline, the logic function being computed is implemented by a pull-down NMOS stack. The input and output validity and neutrality are checked using separate logic gates. The actual computation is combined with data latching, which removes the overhead of explicit registers.

A PCeHB template can take multiple inputs and produce multiple outputs. Figure 2.6 shows a simple two input and one output PCeHB template. *L0* and *L1* are dual-rail inputs to the template and *R* is a dual-rail output. A PCeHB template has a forward latency of two transitions. Each pipeline stage computes logic by using a NMOS pull-down stack followed by an inverter to drive the output.

Figure 2.6: A two input and one output PCeHB template.

To understand the cycle time of 18 transitions in a PCeHB template, let us assume two PCeHB pipelines in series with time (*t*) increments taken in terms of logic transitions.

- At *t* = 0, input tokens arrive at the first PCeHB pipeline block.

- At *t* = 2, first pipeline block produces its output.

- At *t* = 4, second pipeline block produces its output.

- At *t* = 5, *L.e* in the first block goes low.

- At t = 7, L.e in the following block, which is the R.e of the first block, goes low. This indicates that the output from the first pipeline block is no longer needed and can be reset.

- At *t* = 9, *en* signal in the first block is de-asserted.

- At t = 10, \_R rails in the first block are pre-charged.

- At *t* = 11, output, *R*, rails of the first block are reset.

- At *t* = 12, *\_R* rails in the second block are pre-charged.

- At *t* = 14, *L.e* in the first block goes high.

- At *t* = 16, *L.e* in the second pipeline stage goes high. This indicates the neutrality of the inputs in the second pipeline stage.

- At *t* = *18*, *en* is set in the first pipeline block, which indicates that the pipeline is ready to accept new input tokens and compute a new output.

The highlighted logic gates in Figure 2.6 are not used for the actual computation but are only required for the handshake protocol. This includes the generation of completion detection signal (*L.e*) as well as the *en* signal that is used to enable computation or latching in the pipeline stage. For high-througput circuits, each PCeHB stage contains only a small amount of logic with only a few inputs and outputs. As the number of inputs into a PCeHB pipeline stage increases, the input validity tree becomes more complex and may require extra stages to compute, which leads to an increase in the cycle time. The same holds true as the number of outputs increase. Hence, for high-througput circuits each PCeHB stage contains only a small amount of logic with only a few inputs and outputs. This leads to significant handshake overhead, in terms of power consumption and transistor count, as tokens may have to be copied for use in separate processes with each process doing its own validity and neutrality checks.

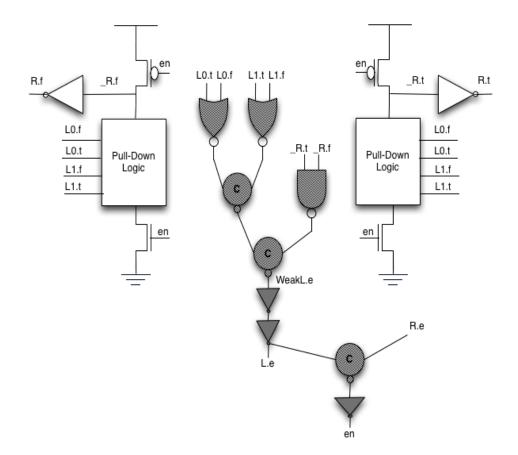

Figure 2.7 shows the power consumption breakdown of a simple full-adder circuit implemented using a PCeHB template. Only 31% of the total power is consumed in the actual logic, while the rest is spent in implementing the hand-shake protocol. This is a significant power overhead, which gets worse as the complexity of PCeHB templates increases with more inputs and outputs. The result in Figure 2.7 was one of the main motivating factors that prompted us to consider alternative pipeline solutions with less handshake circuitry. These alternative templates are discussed and analyzed in great detail in the next chapter.

### 2.4.2 Fine-grain bundled-data pipelines

The fine-grain bundled-data pipelines have an instant area advantage over the QDI pipelines because of their use of single-rail encoded data channels [64]. However, the bundled-data pipelines include far more timing assumptions than QDI circuits which makes them less robust. The bundled-data pipelines contain a separate control circuitry to synchronize data tokens between different

Figure 2.7: Power breakdown of a full-adder circuit in a PCeHB pipeline.

pipeline stages. The control circuitry includes a matched delay line, the delay of which is set to be larger than that of the pipeline's logic delay plus some margin. In [64], for correct operation, the designer has to ensure that the control circuit delay satisfies all set-up and hold time requirements just like in synchronous design. Since our goal was to design pipeline templates with robust timing and with forward latency similar to that of precharged logic, we did not consider any bundled-data pipeline implementations in this thesis.

# Chapter 3

# **Energy-Efficient Pipeline Design**

In this chapter, we present two novel energy-efficient pipeline templates for high throughput asynchronous circuits. The proposed templates, called N-P and N-Inverter pipelines, use single-track handshake protocol. There are multiple stages of logic within each pipeline. The proposed techniques limit handshake overheads associated with input tokens and intermediate logic nodes within a pipeline template. Each template can pack significant amount of logic in a single stage, while still maintaining a fast cycle time of only 18 transitions. Noise and timing robustness constraints of our pipelined circuits are quantified across all process corners. A completion detection scheme based on wide NOR gates is presented, which results in significant latency and energy savings especially as the number of outputs increase.

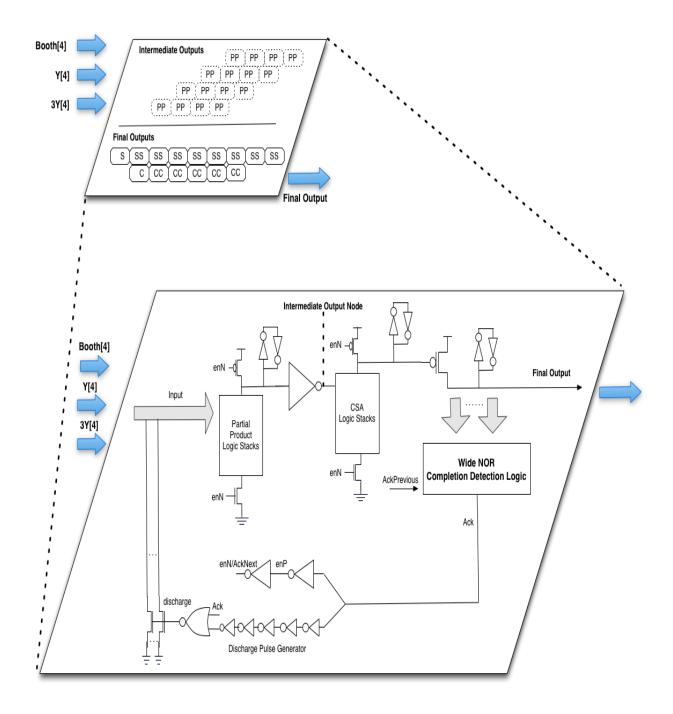

Three separate full transistor-level pipeline implementations of an 8x8-bit booth-encoded array multiplier are presented. Compared to a standard QDI pipeline implementation, the N-Inverter and N-P pipeline implementations reduced the energy-delay product by 38.5% and 44% respectively. The overall multiplier latency was reduced by 20.2% and 18.7%, while the total transistor width was reduced by 35.6% and 46% with N-Inverter and N-P pipeline templates respectively.

## 3.1 Improving Energy-Efficiency of Fine-Grain Pipelines

QDI circuits are robust since each up and down transition within a QDI pipeline template is sensed. But this robustness comes at the cost of significant power consumption in pipeline handshake circuitry as shown in Figure 2.7. The high handshake overhead is one of the serious constraints hampering the wide-range adoption of QDI circuits especially for logic operations with a large number of input and output signals, such as a 32-bit multiplier.

Our goal is to improve the energy efficiency of high performance asynchronous pipelines but without sacrificing robustness. To this end, we kept the following objectives for our resulting pipeline templates:

- Keep the cycle time of each stage within 18 transitions.

- Increase the ratio of logic to handshake. The handshake power overhead must account for less than 50% of total pipeline power.

- No increase in the total transistor count is allowed.

- All timing assumptions are either isochronic fork assumption [41] or have at least the same timing margin as the half-cycle timing assumption [34] according to which the difference in number of transitions between any two delay races must be at least 4.5 transitions.

• Stalls on input and output should not impact correct operation.

We envision these circuits being used for large chunks of local logic (e.g. a multiplier) wrapped with QDI interfaces, rather than globally.

In the past, researchers have tried to increase the logic density of QDI pipelines by adding extra logic stages [8], but this still does not yield the desired reduction in the handshake overhead and leads to an increase in cycle time. To analyze this effect, let us suppose we increase the logic depth of a pipeline by adding extra logic stages. To conform to QDI behavior, the up and down transitions of all newly-created internal signals must be acknowledged. This can be done either by explicitly checking for each transition using completion detection logic as is done in the PCeHB template or using *weak conditions* [62] i.e. the output being valid implies that the input is valid (checked by additional n-fets in the logic stack), and the output being neutral implies that the input is neutral (checked by additional p-fets in the logic stack). The limitations of *weak conditions* for performance are elaborated in [62] [36]. In the case of explicit checking, there is the associated high handshake overhead because of all the extra validity and neutrality detection logic gates. All these extra transitions associated with the newly added logic stages and completion detection logic gates limit energy efficiency gains.

There is clearly a need to look beyond just adding extra logic stages to each pipeline stage. To improve the energy efficiency of high throughput asynchronous pipelines, we look at alternative handshake protocols as well as some timing assumptions in QDI circuits.

#### 3.1.1 Four phase handshake vs. Single-track handshake

In a four phase handshake protocol, the pipeline stage needs to detect the validity and the neutrality of both inputs and outputs. During the second half of the four-phase protocol when the pipeline is waiting for inputs and outputs to be reset, no actual logic is being computed but it still consumes roughly half of the cycle time. Furthermore, the power consumed in detecting the neutrality of inputs and outputs rivals that consumed during their validity detection. Due to these characteristics, the four phase handshake protocol is clearly not an ideal choice for energy efficiency.

Single-track handshake [70] protocol tries to overcome this weakness of four phase protocol by practically eliminating the neutrality phase. Figure 3.1 shows an overview of a single-track handshake protocol. The sender process initiates the communication by sending the data token. The receiver uses the data for computing its logic. Once the data is no longer needed, instead of sending an acknowledge signal back to the sender process, the receiver process resets the input tokens itself by pulling the data wires low through NMOS transistors as illustrated in Figure 3.1. There are as many NMOS discharge transistors as there are data wires, but for simplicity we show only one discharge transistor in Figure 3.1. As the data wires pulled low, the sender detects the token consumption and gets ready to send the next token. Hence, eliminating the transitions associated with second part of the four phase protocol.

There has been very limited work on single-track handshake templates. Most of the prior work has focused on using single-track handshake protocol to reduce the cycle time of asynchronous pipelines to less than 10 transitions and not on how to use these extra transitions to improve logic density and en-

Figure 3.1: Single-track handshake protocol.

ergy efficiency. Ferretti et al [24] provide a family of asynchronous pipeline templates based on single-track handshake protocol. Just like high throughput QDI circuits, each of their pipeline templates contains only a small amount of logic. Furthermore, their 6-transition cycle time pipelines use some very tight timing margins that may require significant post-layout analog verification. Singletrack circuits have been used in the control path of GasP [64] bundled-data pipelines. However, the actual data path of the pipeline does not use a singletrack handshake protocol.

We employ single-track handshake protocol for our proposed pipeline templates. However, our design effort focuses on increasing the logic density and energy efficiency of each pipeline stage and not on reducing cycle time.

## 3.1.2 Relative Path Timing Assumption

QDI circuits are highly tolerant of process variations as each transition within a QDI pipeline is sensed. The isochronic fork assumption [41], which states that

the difference in delay between branches of a wire is insignificant compared to the gate delays of the logic reading their values, is the only timing assumption allowed in QDI design. Recently, LaFrieda et al [34] exposed another timing assumption that is quite commonly used in QDI implementations, which they named as the half cycle timing assumption (HCTA). According to HCTA, the difference in number of transitions between any two delay races must be at least 4.5 transitions for PCeHB-style templates. The resulting templates are referred to as Relaxed QDI templates and are shown to be quite robust.

LaFrieda et al [34] exploited HCTA to improve energy efficiency of their four phase handshake protocol pipelines. In this work, we look to improve energy efficiency of single track handshake protocol pipelines by introducing timing assumptions with a margin of at least 5 gate transitions between any two relative delay races.

## 3.2 High Throughput Energy Efficient Pipeline Templates

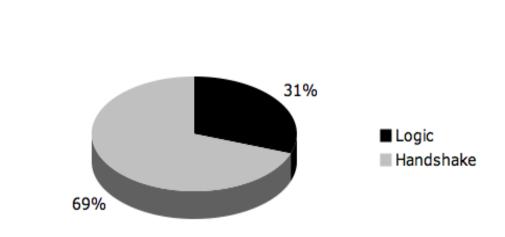

#### 3.2.1 N-P and N-Inverter Pipeline Templates

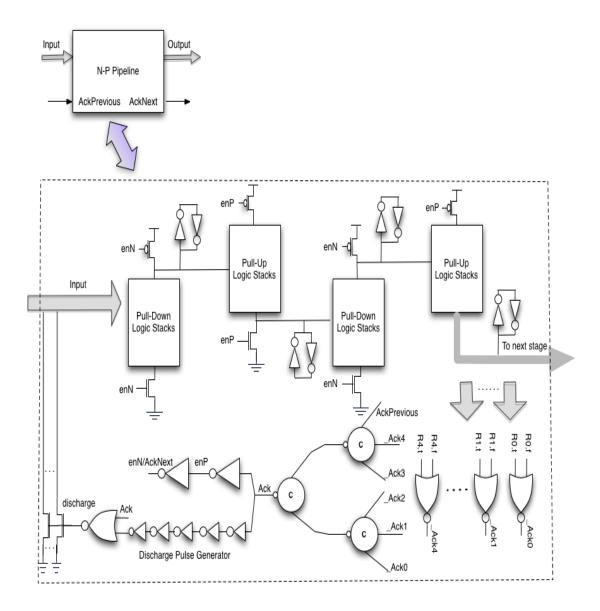

We use single-track handshake protocol for our proposed pipeline templates. Figure 3.2 shows the gate-level depiction of our first proposed template with 5 arbitrary dual-rail outputs indicated by signals *R0* to *R4*. We have named the template N-P pipeline since it computes logic using NMOS pull-down and PMOS pull-up stacks. Each NMOS and PMOS stage can comprise multiple logic stacks. However, for simplicity, we do not show multiple logic stacks and global reset signals.

Figure 3.2: N-P pipeline template

A PCeHB template has two logic stages per each pipeline, with the second logic stage comprising an inverter to drive the output rails. Hence, there is only one effective logic computation per pipeline block. In contrast, the N-P template has *N* arbitrary stages of actual logic computations. However, for ease of explanation and to keep cycle time within 18 transitions, we use N-P pipelines

with four stages of logic. In the reset state, the NMOS logic nodes in the pipeline are precharged, whereas the PMOS logic nodes are pre-discharged. Each stateholding gate includes a staticizer, which comprises a keeper and a weak feedback inverter, to ensure that charge would not drift even if the pipeline were stalled in an arbitrary state. The staticizers, drawn as two cross-coupled inverters, for the intermediate as well as the final output nodes are shown in Figure 3.2.

When 1-of-N encoded input tokens arrive, logic is computed in the first stage by pulling down the precharged nodes. This is similar to how logic is computed in QDI templates. We limit the number of series transistors in an NMOS stack to a total of four. The second logic stage uses a stack of PMOS transistors to compute logic by pulling up the pre-discharged nodes. As the PMOS transistors have slower rise times, for throughput purposes we limit the number of series transistors in a PMOS stack to a total of three (including the enable). As the output nodes from the second stage pull up, the pull-down stacks in the third stage get activated and compute logic by pulling down their output nodes. Finally, the fourth stage computes logic by using its pull-up stack of PMOS transistors. The four cascaded stages of logic in our pipeline are similar to cascaded domino logic but without any static inverters in between dynamic logic stages.

There are no explicit validity detection gates for the arriving input tokens nor for any intermediate outputs that are being produced. *AckPrevious* (explained later in this section) signifies the validity of input tokens into the pipeline and alleviates the need to explicitly check for validity. For intermediate outputs produced and consumed within the template, validity must be embedded in a pullup or pull-down logic stack that uses the intermediate output to compute the following stage logic output. This could incur additional cost, depending on the function being implemented. However, for a logic stack inherently embedded with input validity, for example a stack that computes the sum of two inputs, there is zero validity detection overhead. The elimination of explicit validity detection gates for input tokens and intermediate output nodes leads to considerable power savings and minimization of handshake overhead.

There is an explicit completion detection logic for all the outputs that eventually leave the pipeline, either at the end of the second stage or the fourth stage. The completion detection of the final outputs automatically signifies the validity of all intermediate outputs as well as that of all the initial input tokens into the N-P pipeline. The completion detection logic comprises a set of NOR gates and a c-element tree as shown in Figure 3.2. Each of the c-element gates includes a staticizer in parallel. These staticizers are not shown for simplicity. The outputs from the NOR gates are combined using a c-element tree which de-asserts the Ack signal once all outputs are valid. This leads the discharge signal to go high, which initiates the reset of all input tokens. The discharge signal is only set for a short pulse duration. The de-asserted *Ack* signal also sets the *enP* signal to high which discharges all pull-up nodes in logic stage two. The *enN* signal is set low, which precharges all pull-down nodes in logic stages one and three. Since the neutrality of the internal nodes is not sensed, we introduce a timing assumption on their transition. The discharge of input tokens with a short pulse signal introduces another timing assumption. These two timing assumptions entail the following constraints:

• The pull-down nodes must be fully precharged before *enN* goes high and pull-up nodes must be fully discharged before *enP* transitions low. This

translates into a race condition of 1 pull-up/pull-down transition versus 9 gate transitions, the minimum transition count before both *enN* and *enP* flip when two N-P pipelines are in series.

• All input tokens must be fully discharged within the short pulse discharge period. The pulse has a minimum period of 5 gate transitions. There are as many NMOS discharge transistors as there are input data rails.

The robustness of our pipeline template is not compromised as these timing assumptions satisfy the minimum timing constraint of at least 5 gate transitions between any two relative path delay races.

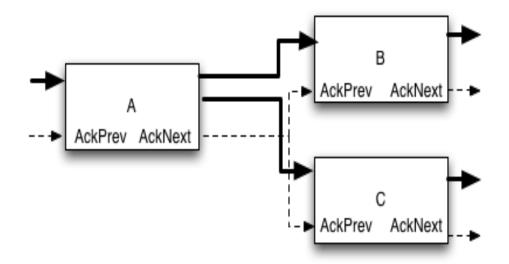

The discharge of any of the outputs before the validity of all other outputs has been acknowledged can permanently stall the pipeline. To analyze this effect, let us suppose we have three N-P pipelines A, B, and C as shown in Figure 3.3. A produces two outputs, one of which goes to B and the other one to C. B uses the output from A to compute its output. Since B has computed its output, it can now discharge the input it received from A. If A's other output, which is headed for C, is not yet produced or acknowledged by the completion detection logic of A, then B's discharge of its input will make the completion detection logic of A unstable. To prevent this, we add the AckNext signal to our pipeline template. It is sent to all following pipeline stages that consume the outputs from the current N-P pipeline. This signal is referred to as *AckPrevious* in the destination pipeline as shown in Figure 3.2. It prevents the discharge of the tokens coming from the sender stage before the validity of all outputs in the sender has been acknowledged. As mentioned earlier, *AckPrevious* also signifies the validity of input tokens into the pipeline, hence alleviating the need to check for input token validity in NMOS pull-down stacks. In the case where inputs come from more than one pipeline block, the *AckPrevious* signals from all corresponding pipeline blocks need to be added to the completion detection logic to ensure against any premature discharge of input data rails.

Figure 3.3: Ack signals to ensure correctness

Forking of an output to two successors is also not allowed because then the two successors can reset (discharge) the connection at different times, which could lead to potential conflicts. Hence, we need to create explicit duplicate outputs in the last logic stack for each output that goes to multiple destinations.

To determine the cycle time of the proposed N-P pipeline, let us assume two N-P pipelines in series with time (*t*) increments taken in terms of logic transitions.

- At *t* = 0, input tokens arrive at the first pipeline block.

- At *t* = 4, first pipeline block produces its output.

- At *t* = 7, *Ack* signal in the first block is de-asserted which signifies the validity of all output signals

- At *t* = 8, second pipeline block produces its output.

- At t = 9, input tokens in the first pipeline block are discharged. Internal PMOS logic nodes are discharged.

- At *t* = 10, NMOS logic nodes in the first pipeline are precharged.

- At *t* = 13, output tokens from the first pipeline block are discharged by the second pipeline.

- At *t* = 16, *Ack* signal in the first block is asserted which signifies the reset of all output signals.

- At *t* = 18, *enN* is set and the pipeline is ready to accept new input tokens.

Hence, our proposed N-P pipeline has a cycle time of 18 transitions. Stalls on inputs and outputs do not impact correct operation. The template waits in its present state if inputs arrive at different times. This holds true for outputs being computed at different times as well. The relative path delay assumption has a root, *Ack*, which only changes after all inputs have arrived and all outputs have been computed. As a result, correct operation is not a function of arrival time of signals, which makes the N-P template quite robust.

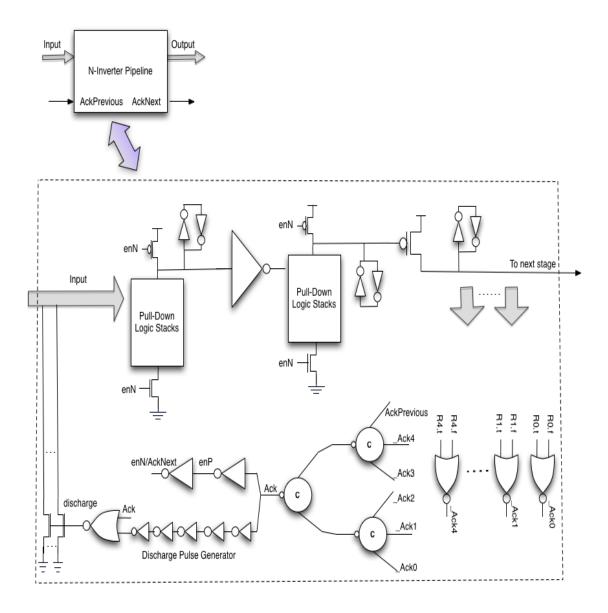

We could invert the senses of the inputs and outputs by changing the order of the logic stacks within N-P pipeline. With inverted inputs, the first stage comprises PMOS logic stacks and the final logic stage comprises NMOS logic stacks with the outputs produced in inverted sense. This could improve the drive strength of the output signals especially in the case of high fan-out. Our second proposed pipeline template replaces the PMOS pull-up logic stacks in stage 2 with an inverter, hence the name N-Inverter template, and includes only a single pull-up PMOS transistor in stage 4 as shown in Figure 3.4. As PMOS logic stacks have slower rise times and relatively weak drive strength, the N-P template cycle time may incur a performance hit. The N-Inverter template addresses this by using inverters with faster switching time and strong drive strength . It also results in better noise margins as discussed in detail in Section 3.3. However, these improvements come at the cost of reduced logic density as stage 2 and 4 no longer perform any effective logic computation. Despite these alterations, the N-Inverter and N-P templates use exactly the same timing assumptions. The completion detection and handshake circuitry is also identical.

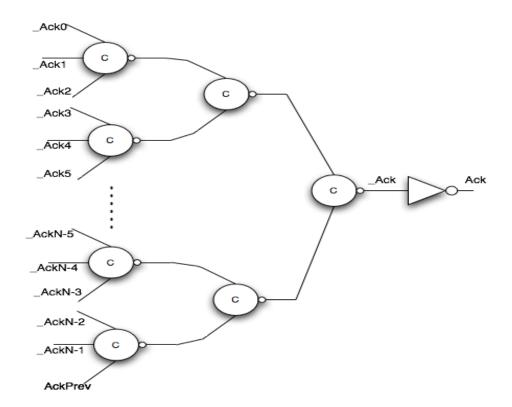

### 3.2.2 Completion detection logic for large number of outputs

Since N-P and N-Inverter pipeline templates can pack significant logic in a single pipeline block, there may be cases where a pipeline block has quite a large number of outputs. To detect the validity of these large number of outputs, we may have to expand the c-element validity tree by a couple of extra stages as shown in Figure 3.5.

As a result of these two extra stages in the completion detection validity tree, the cycle time of N-P and N-Inverter templates is no longer 18 transitions. There are four extra transitions, two each for the validity and neutrality detection of the output signals, which increases the cycle time to 22 transitions. Since our goal was to keep the cycle time within 18 transitions, we explored a number of

Figure 3.4: N-Inverter pipeline template

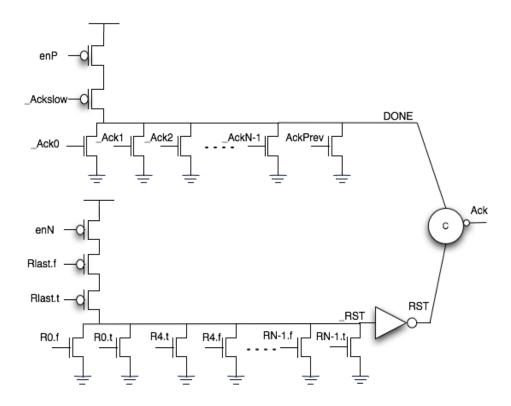

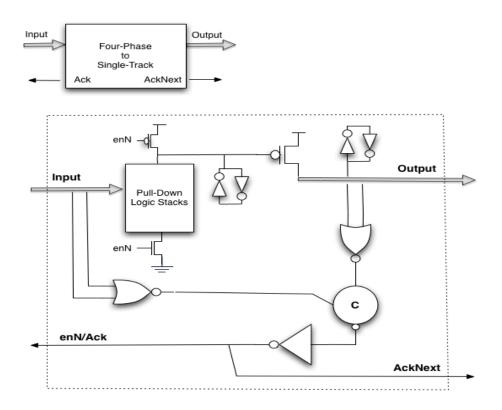

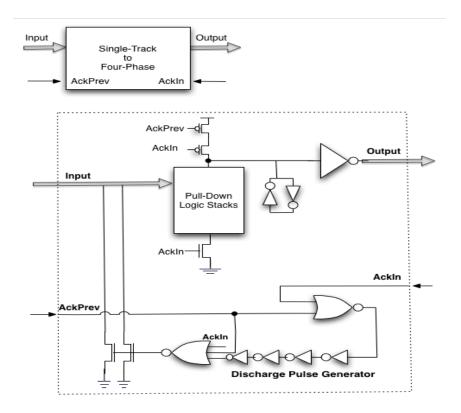

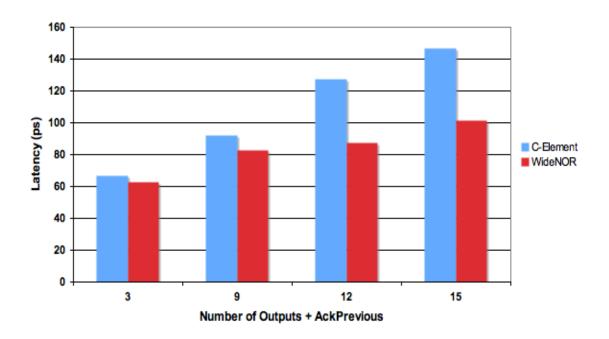

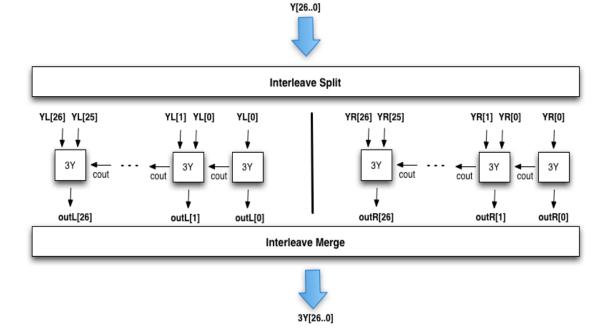

other completion detection circuits [56] [14]. To reduce the cycle time back to 18 transitions, we use wide NOR gates based completion detection circuitry as proposed in [14], but with a couple of optimizations to make the circuitry feasible for our proposed pipeline templates. These optimizations include the use of only one output from the set of outputs destined for the same next pipeline