# HyperFlow: A Processor Architecture for Timing-Safe Information-Flow Security

Andrew Ferraiuolo, Mark Zhao, Andrew C. Myers, G. Edward Suh Cornell University Ithaca, NY 14850, USA

af433@cornell.edu, yz424@cornell.edu, andru@cs.cornell.edu, suh@ece.cornell.edu

Abstract—This paper presents HyperFlow, a processor that enforces secure information flow, including control over timing channels. The design and implementation of HyperFlow offer security assurance because it is implemented using a security-typed hardware description language that enforces secure information flow. Unlike prior information-flow secured processors that aim to strictly enforce noninterference, HyperFlow supports complex information flow policies that can be configured at run time, and provides support for secure interprocess communication (IPC) and system calls. The architecture also offers a new model for process isolation in which memory protection is provided via information flow control with strong security assurance while allowing IPC and shared memory. HyperFlow is designed to support practical applications and system architectures. It therefore supports decentralized information flow mechanisms that allow controlled communication among mutually distrusting processes. mediated by dynamic, fine-grained labels. Static informationflow verification of such a complex processor architecture poses significant challenges, which require contributions in both the hardware architecture and the security type system. The paper discusses the architecture decisions that make the processor secure and describes a new secure HDL, named ChiselFlow, that allows these decisions to be verified in a lightweight way. The HyperFlow architecture is also prototyped on a fully-featured processor that offers a complete RISC-V instruction set, and is shown to have moderate overhead on area and performance.

#### I. INTRODUCTION

In modern computer systems, hardware plays a central role in providing isolation for software modules. Protection rings are widely used to isolate supervisor processes from user processes. Recent hardware security architectures such as ARM TrustZone [23] and Intel SGX [8] aim to protect critical software even when the operating system is malicious or compromised. However, the security of these processors relies on the assumption that the underlying hardware properly enforces necessary security properties.

Unfortunately, microprocessors often contain vulnerabilities that allow security-critical software to be compromised by untrusted software. Software-exploitable vulnerabilities in SGX have already been found [24]. Previous studies found vulnerabilities in implementations of Intel VT-d [38] and system management mode (SMM) [37]. Moreover, the recent Spectre [19] and Meltdown [22] vulnerabilities show that even if the hardware is correct in a conventional sense—that it implements a specification—is not sufficient to ensure security. Exploiting subtle timing channels in Intel microprocessors, Meltdown can be used to leak arbitrary kernel data. Therefore,

it is important for security to ensure that hardware implementations are free of timing channels.

Prior work has shown that hardware constructed with a security-typed hardware description language (HDL) [20], [43] can provide strong security assurance. Security-typed HDLs can statically prove that the hardware prevents insecure information flows: untrusted signals cannot affect trusted signals, and secret signals cannot affect public ones. Because HDLs produce cycle-level descriptions of the hardware, security-typed HDLs can also prove that the hardware is free of timing channels. Prior work has also shown that security-typed HDLs catch real-world security vulnerabilities [14].

This paper presents HyperFlow, a processor architecture and implementation designed for information-flow security that is verified with a security-typed HDL at design time, providing strong security assurance about its design and implementation. The HyperFlow architecture is carefully designed to remove all disallowed information flows between security levels, including timing channels, and the information flows within the design are statically verified using a security type system. HyperFlow is also implemented as an extension of a fully featured processor with a complete (RISC-V) instruction set.

HyperFlow security policies. Beyond being a practical, realistic processor, HyperFlow also innovates in the security policies it enforces. Unlike prior processors with verified information flow, which only supported simple, fixed 2-point or 4-point policy lattices, HyperFlow can enforce complex application-defined security policies directly in hardware, in line with work on information-flow security in operating systems and programming languages which suggests that real applications need rich lattice policies that can capture complex trust relationships among mutually distrusting principals [5], [12], [26], [41].

We show how to encode complex and dynamic security policies involving both confidentiality and integrity even for applications built from communicating processes serving mutually distrusting principals. By enforcing security policies in hardware, the software component of the trusted computing base is minimized, and strong security assurance is obtained. While practical tagged architectures have previously been built with the ability to encode information flow policies [11], [42], they do not handle timing channels, and their implementations have not been secured with an information flow HDL.

HyperFlow represents rich lattice policies in hardware at the

bit level by introducing *hypercube labels*, in which software-level labels are mapped to points in a hypercube. Hypercube labels enable efficient comparisons between security levels directly in hardware, and they are amenable to static checking in the security-typed HDL.

Controlled downgrading. To be practical, systems based on information-flow security must allow exceptions to noninterference [16]. For example, applications must be able to release the results of computing on secrets. This can be accomplished by downgrading, a mechanism for relaxing information-flow policies. Uncontrolled downgrading is dangerous, so the HyperFlow ISA provides instructions for controlled downgrading. Downgrading of confidentiality policies (declassification) is permitted only when it is *robust* [39]secrets can be released only if the downgrade can be influenced only by the owners of these secrets. Dually, downgrading of integrity policies (endorsement) is permitted only it when it is transparent [4]: that is, if the party providing the endorsed data could have read it. Together, these conditions ensure that information flow is nonmalleable. Nonmalleable information flow is enforced not only at the ISA level but also at the HDL level, providing similarly strong assurance about the implementation.

Secure interprocess communication. Another novel and challenging feature of HyperFlow is its support for secure communication across trust domains. HyperFlow allows but constrains interprocess communication (IPC) via shared memory. It also supports the secure communication via registers of arguments and return values of system calls. System calls and shared function libraries present another challenge that HyperFlow addresses—both scenarios require a mechanism by which untrusted code can invoke trusted code. HyperFlow introduces an information-flow secure *call gate* [31], [36] mechanism to make cross-domain control transfers secure.

Memory protection. Conventional systems use virtual memory to isolate pages that belong to different applications. However, hardware support for virtual memory is complex and its correctness also depends on other mechanisms such as cache coherence, which is notoriously difficult to implement correctly. HyperFlow replaces conventional memory protection with *security tags* associated with each physical page (or frame) of memory. Security tags are mapped to hypercube labels using a mapping defined by the operating system; accesses to memory are then mediated using hypercube labels. The security of this mechanism is checked in the HDL code at design time. Despite its novel mechanism for memory protection, HyperFlow also provides a virtual-memory interface to support existing operating systems and applications.

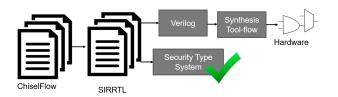

ChiselFlow security-typed HDL. To ease the task of information-flow verification, we designed a security-typed HDL called ChiselFlow in which to construct HyperFlow. ChiselFlow is embedded in Scala, and inherits the expressiveness of a complex full-featured language. But ChiselFlow compiles to a small intermediate language that is responsible for the enforcement of security policies, so the trusted component of ChiselFlow is small. Unlike prior secure HDLs, ChiselFlow

provides label inference that reduces programmer effort. The hardware designer provides security labels for the inputs and outputs of hardware modules, but labels of internal signals can be omitted. ChiselFlow also supports multiple mechanisms for describing heterogeneously labeled data structures, which are crucial for practical designs. Finally, ChiselFlow separates the confidentiality and integrity components of labels supporting controlled downgrading.

**Prototype implementation.** We implement HyperFlow as an extension to the RISC-V Rocket processor, and HyperFlow supports a complete RISC-V ISA. Our implementation allows conventional virtual-memory protection to interoperate with HyperFlow's information flow protection. HyperFlow implements performance-critical features that were absent in prior processors secured with an IFC HDL. The prototype implementation shows that the new security features in HyperFlow add moderate area overhead, largely due to the additional storage for security tags, and moderate performance overhead due to timing-channel protection. The HyperFlow implementation is also more fully-featured than prior information-flow secured processors. The timing-safe implementations of these features also type-checks with ChiselFlow, providing strong assurance that the implementation is secure.

#### II. HDL-LEVEL INFORMATION FLOW CONTROL

Implementing hardware with security-typed hardware description languages (HDLs) is a promising approach to ensuring the hardware is secure. HDL-level information flow control applies techniques from language-based security [29] to hardware design [13], [20], [21], [43]. Variables in the code that describe the hardware design are annotated with security labels, L, which are types describing restrictions on where information contained in that signal can flow. The type system then enforces these restrictions.

Type systems for information flow security can enforce noninterference [16], which ensures that a signal with a label L can only be influenced by signals with labels that are less restrictive than L. For example, if the label public is less restrictive than the label secret, then a secret signal cannot influence a public signal. When a label L is no more restrictive than another label L', it is said that L flows to L', written  $L \sqsubseteq L'$ .

HDLs for information flow security can enforce a particularly strong, timing-safe variation of noninterference [21], [43]. HDLs describe hardware at the register transfer level (RTL) – the code describes new valuations of signals during each clock cycle. Because HDLs give cycle-level descriptions of hardware, the information flow type system can guarantee cycle-level timing-channel freedom.

In this work, we develop a new information-flow-secure HDL, ChiselFlow, and use it to construct a novel and secure processor. ChiselFlow extends Chisel [3], an HDL embedded in Scala. An advantage of the ChiselFlow implementation is that it gains much of the expressiveness of Scala without including this complex language in its trusted computing base. Like Chisel, ChiselFlow generates a simpler, compiled

```

class ExampleIO extends Bundle {

val id = Input(UInt(4.W), L(public, trusted))

val data_in = Input(UInt(32.W), hlvl(id, id))

val data_out = Output(UInt(32.W), hlvl(id, id))

}

class ExampleModule extends Module {

val io = IO(new ExampleIO)

val secretMask = Reg(init = 0x2.U, L(secret, trusted))

val publicMask = Reg(init = 0x1.U, L(public, trusted))

when (id confFlowsTo secret) {

io.data_out := secretMask & io.data_in

}.otherwise {

io.data_out := publicMask & io.data_in

}

}

```

Fig. 1. ChiselFlow example.

intermediate representation that can then be used to produce hardware designs. The intermediate representation (IR) for ChiselFlow is called SIRRTL; it extends Chisel's IR, FIR-RTL, with information flow annotations. The enforcement mechanisms of ChiselFlow operate entirely on SIRRTL. In an accompanying technical report [1], we formalize a core subset of SIRRTL and prove that, aside from downgrades, well-typed hardware modules enforce timing-sensitive noninterference. In Appendix A, we discuss the implementation of ChiselFlow and some features that were useful for implementing HyperFlow securely.

Figure 1 shows an example of ChiselFlow code, which looks much like Chisel code aside from the parts in bold font. As in Chisel, ChiselFlow describes hardware modules with classes that extend Module. The example shows a module called ExampleModule, which takes two inputs: data\_in, a data value, and id, a one-bit flag indicating whether data\_in is secret or public. The module outputs data\_out, which is data\_in masked with a secret value when id indicates that data\_out can observe secrets.

Signals in ChiselFlow are annotated with security labels that have confidentiality and integrity components. Here, the label L(public,trusted) means that id is fully public and fully trusted. However, ChiselFlow also supports software-defined security policies that depend on the run-time values of variables. The ability to express security policies that change at run time enables hardware implementations with low area overhead, because it allows hardware modules to be shared among security domains over time. For example, hlvl(id, id) describes the interpretation of the signal id as an information flow label. Although labels of this form can depend on run-time values of signals, the type system relies on a static program analysis to reason about the behavior of these run-time types at design time.

The interface for ExampleModule is ExampleIO, which describes a record type in which id, data\_in, and data\_out are records with distinct security labels that have already been described. The register secretMask is a fully secret and fully trusted register. The body of ExampleModule is secure because access control ensures that the value of secretMask does not flow to io.data\_out unless id flows to secret. The program analysis statically determines that under the branch in which

this access control is true, the security label of io.data\_out is secret, which permits the assignment from the value that depends on the secret.

#### III. SECURITY POLICIES IN HYPERFLOW

HyperFlow enforces information flow security policies directly in hardware. Prior work on label models for information flow security has developed rich policies allow mutually distrusting principals to communicate [5], [12], [26], [41]. These label models represent policies using lattices of information flow labels. HyperFlow can enforce policies described in these models because it can enforce general lattice-based policies.

# A. Confidentiality and integrity policies

Information flow labels in HyperFlow support reasoning about both confidentiality and integrity. An information flow label  $\ell = (c, i)$  in HyperFlow is a pair of a confidentiality level c and an integrity level i. Confidentiality and integrity levels in HyperFlow both form lattices that are ordered by  $\sqsubseteq_C$  and  $\sqsubseteq_I$  respectively. The ordering on confidentiality levels specifies constraints on secrecy; if  $c \sqsubseteq_C c'$ , then c is no more confidential than c'. Similarly, if  $i \sqsubseteq_I i'$ , then i is at least as trustworthy as i'. The ordering of integrity levels and confidentiality levels is dual: high confidentiality levels are more restrictive than low ones, whereas low integrity levels are more restrictive than high ones. The orderings on confidentiality and integrity levels are lifted to a lattice of labels  $\sqsubseteq$ ; if  $c \sqsubseteq_C c'$  and  $i \sqsubseteq_I i'$  then  $(c,i) \sqsubseteq (c',i')$ . We write  $C(\ell)$  and  $I(\ell)$  to denote just the confidentiality or integrity part of the label respectively.

#### B. Lattices via bit vectors

In order to support efficient computations and comparisons of labels in hardware, HyperFlow represents lattices over bit vectors. We first explain the ordering of confidentiality levels. Levels are mapped to a point in a hypercube, which is expressed using a bit vector. A bit vector b is split into  $d \in D$  dimensions, each of K bits. Bit vectors are then functions from [1, D] to  $[0, 2^K - 1]$ , and the notation b(i)represents the value in the  $i^{th}$  dimension of b. Bit vectors  $b_1$  and  $b_2$  are ordered in the confidentiality lattice, written  $b_1 \sqsubseteq_C b_2$  if each dimension of  $b_1$  is numerically less than or equal to the corresponding element of  $b_2$ . The join  $(\sqcup_C)$  and meet  $(\sqcap_C)$  of two confidentiality components are respectively computed by taking the maximum or the minimum over the corresponding dimensions of each vector. The lattice over bit vectors is defined more formally in Figure 2. As an example, if  $b_1$  and  $b_2$  are each bit vectors of 4, 2-bit dimensions, and  $b_1$  is 10100111 and  $b_2$  is 10010010, then  $b_2 \sqsubseteq_C b_1$ . It is straightforward to check that this order has lattice properties (i.e., it is a transitive, reflexive, and antisymmetric partial order). The ordering in the integrity lattice is exactly dual to the ordering in the confidentiality lattice as shown in Figure 3.

We write  $(c,i) \sqcup (c',i') \triangleq (c \sqcup_C c',i \sqcup_I i')$  and  $(c,i) \sqcap (c',i') \triangleq (c \sqcap_C c',i \sqcap_I i')$  to denote the join and meet over labels respectively. We use  $\top$  and  $\bot$  to denote a sequence of all 1's and

$$b \in B = [1, D] \to [0, 2^K - 1]$$

$$b_1 \sqsubseteq_C b_2 \triangleq \forall d \in [1, D].b_1(d) \le b_2(d)$$

$$(b_1 \sqcup_C b_2)d \triangleq \max\{b_1(d), b_2(d)\}$$

$$(b_1 \sqcap_C b_2)d \triangleq \min\{b_1(d), b_2(d)\}$$

Fig. 2. Confidentiality ordering over bitvectors.

$$b \in B = [1, D] \to [0, 2^K - 1]$$

$$b_1 \sqsubseteq_I b_2 \triangleq \forall d \in [1, D]. b_1(d) \ge b_2(d)$$

$$(b_1 \sqcup_I b_2)d \triangleq \min\{b_1(d), b_2(d)\}$$

$$(b_1 \sqcap_I b_2)d \triangleq \max\{b_1(d), b_2(d)\}$$

Fig. 3. Integrity ordering over bitvectors.

all  $\emptyset$ 's respectively. In the confidentiality order,  $\top$  and  $\bot$  are completely secret and completely public respectively. In the integrity order,  $\top$  and  $\bot$  are completely trusted and completely untrusted respectively. The labels  $(\bot, \top)$  and  $(\top, \bot)$  are the least and most restrictive labels in information flow order  $(\sqsubseteq)$ .

Other representations of lattices in computer systems have been studied [15]. Because HyperFlow uses information flow labels for access control and timing-channel protection, lattice comparisons and computations need to be done throughout the implementation, and the ability to efficiently update and compare labels directly in hardware is particularly important in designing a processor with strong information flow security. Prior representations of lattices such as adjacency lists and matrices are less space-efficient. Other approaches that rely on caching requires software intervention on each lattice operation. The hypercube lattice is most similar to the skeletal representation, also known as the Fidge and Mattern vector clock [18]. However, vector clocks have not been used to represent lattices in hardware in prior work.

# C. Nonmalleable downgrading

Systems for information flow control are often intended to enforce noninterference, which prevents all information flows that violate lattice policies. However, noninterference is too restrictive for practical systems. For example, data computed using secrets may eventually need to be released publicly. Noninterference may be weakened through *downgrading* which relaxes information flow labels. Downgrading that weakens confidentiality is said to *declassify* whereas downgrading that weakens integrity is said to *endorse* [40].

Because downgrading weakens noninterference, effort has been made to constrain downgrading to limit its potential to cause harm [30]. In this work, we permit communication that weakens noninterference as long as the downgrading it causes is nonmalleable [4]. Nonmalleable information flow subsumes two security conditions, robust declassification and transparent endorsement. These security conditions have not been enforced by previous hardware mechanisms.

Robust declassification [39] only permits information to be downgraded by parties that have authority over that information. As in prior work on defining robust declassification [4], [6], authority (trust, privilege) is represented by integrity; only

a principal at least as trusted as I(p) can declassify data with confidentiality C(p). This constraint is useful for decentralized systems. A principal A can declassify its data to a principal B, and as long as B does not have integrity I(A), B can observe A's data but is prevented from releasing it elsewhere.

In HyperFlow, a process with label  $\ell_{cur}$  can declassify a label  $\ell$  to  $\ell'$  only if the following holds:

$$C(\ell) \sqsubseteq_C C(\ell') \sqcup_C (I(\ell_{cur}) \sqcup_I I(\ell)).$$

This condition follows directly from prior work on defining robust declassification in the context of programming languages [4], [6]. Roughly, it allows the confidentiality  $C(\ell)$  of the data being declassified to be "made up for" by the integrity  $I(\ell)$  of the data being declassified and the integrity  $I(\ell_{cur})$  of the current process. When  $\ell$  can be robustly declassified to  $\ell'$  by a process with label  $\ell_{cur}$ , we write  $\ell \stackrel{C}{\longleftarrow} \ell'$ .

The dual of robust declassification is transparent endorsement [4]. It sets a maximum confidentiality on endorsements to prevent opaque writes that could enable attacks. A write is opaque if a principal could have written data but not read it. In HyperFlow, a process with label  $\ell_{cur}$  can endorse a label  $\ell$  to  $\ell'$  if,

$$I(\ell) \sqsubseteq_I I(\ell') \sqcup_I (C(\ell_{cur}) \sqcup_C C(\ell)).$$

This condition follows directly from work on defining transparent endorsement for a functional programming language [4]. When  $\ell$  can be transparently endorsed to  $\ell'$  by a process with label  $\ell_{cur}$ , we write  $\ell$   $\xrightarrow[\ell_{cur}]{I} \ell'$ . When  $\ell$   $\xrightarrow[\ell_{cur}]{I} \ell'$  and  $\ell$   $\xrightarrow[\ell_{cur}]{C} \ell'$  we say that  $\ell$  can be nonmalleably downgraded to  $\ell'$  by a process with label  $\ell_{cur}$  and we write  $\ell$   $\xrightarrow[\ell_{cur}]{C} \ell'$  [4].

#### IV. THE HYPERFLOW ARCHITECTURE

HyperFlow is realized as a tagged architecture where security labels are explicitly represented as hardware tags for a process, registers, and memory pages. HyperFlow replaces conventional memory protection enforced by virtual memory with security tags that are associated with each physical page (or frame) of memory. Tagged physical memory enables static checking of information flow with a type system. Virtual memory does not ensure noninterference; it is possible for the same physical page to be mapped to virtual addresses owned by distrusting processes. Even if the mapping did ensure noninterference, it would not be possible to prove that noninterference is established purely by inspecting the hardware design, since the mapping is software-defined. The tagged physical memory can also be used to reduce the software trusted computing base by removing the need to rely on virtual memory for process isolation.

The security tags in HyperFlow are information flow labels. By enforcing information flow labels in hardware, HyperFlow can permit isolation among multiple principals that are mutually distrusting, yet communicate. Noninterference precludes communication among mutually distrusting principals, so the information that they are communicating must be downgraded.

However, HyperFlow constrains these downgrades by ensuring that they are nonmalleable [4]. In doing so, HyperFlow ensures that processes cannot leak information that they do not have authority over. Enforcing nonmalleability requires the ability to inspect the integrity and confidentiality of the information being downgraded as well as the principal initiating the downgrading. This is accomplished by making the information flow labels visible in hardware.

## A. Process levels

Processes executing in HyperFlow are associated with a level,  $\ell_{cur}$ . The level  $C(\ell_{cur})$  represents the greatest level of secrecy that the process can observe, and  $I(\ell_{cur})$  represents the most trusted level of information it can affect. In order for the currently executing process to read a page of memory, m, we require  $\mathcal{M}_{\ell}(m) \sqsubseteq \ell_{cur}$ , where  $\mathcal{M}_{\ell}$  is a mapping from pages to their information flow labels. Similarly, to write to m, we require that  $\ell_{cur} \sqsubseteq \mathcal{M}_{\ell}(m)$ .

HyperFlow also associates security labels with registers to facilitate two kinds of communication that are needed in processors: 1) communication between userspace applications and the operating system during system calls, and 2) interprocess communication in memory. During system calls, arguments and return values are communicated between the application and system call handler via registers. HyperFlow permits communication using registers by associating labels with registers and through instructions that downgrade registers' labels. Assuming the application is untrusted, the trusted call handler can endorse the registers storing the arguments after inspecting them. At the end of the system call, the call handler can declassify the registers storing the return values before re-entering the public application.

Because information flow labels are used to enforce security, HyperFlow must ensure that the labels accurately reflect the security of the data they protect. General-purpose register r has security label  $\ell_r$ . Normally, to store the content of r to an address in m, we require  $\ell_r \sqsubseteq \mathcal{M}_{\ell}(m)$ . Similarly, loading a word from m into r requires  $\mathcal{M}_{\ell}(m) \sqsubseteq \ell_r$ .

Though secure, these invariants sometimes prevent necessary communication among distrusting principals. Hyper-Flow permits interprocess communication among distrusting principals via shared memory so that it provides a familiar software interface. Writes to and reads from shared memory that would violate noninterference require downgrading. Pages can be downgraded; however, downgrading an entire page is too imprecise for many applications. HyperFlow supports downgrades at the granularity of an individual word with downgrading load and store instructions. These instructions work just like conventional loads and stores except that they downgrade the source data while it is copied. HyperFlow also supports page downgrades for zero-copy sharing of entire pages.

Processes in HyperFlow are also protected against information flow violations caused by the instructions that are fetched by the currently executing process. The active process should not execute low-integrity instructions because this would allow adversaries that the process does not trust to influence the code that the process executes. Similarly, branching conditions that depend on secrets can cause secrets to be released through the instructions that HyperFlow executes. Information leaks through control flow are called *implicit flows*.

HyperFlow prevents implicit flows because  $\ell_{cur}$  also represents the information flow label of the most recently fetched instruction. Branches cannot depend on a register r unless  $\ell_r \sqsubseteq \ell_{cur}$ . Similarly, for all instructions that write to a register r, HyperFlow requires  $\ell_{cur} \sqsubseteq \ell_r$  to ensure that the label of  $\ell_r$  accurately reflects the process that influenced it.

#### B. Information-flow call gates

The restriction on branch conditions and on writes to registers together prevent an untrusted or secret process from invoking code that is trusted or public. However, untrusted applications need to be able to call trusted code when making system calls, and secret applications need to be able to call public functions from libraries. HyperFlow securely supports control transfers of this form with a mechanism that is analogous to call gates that originated in Multics [31]. Call gates in HyperFlow tightly couple the entry point (program counter) that initiates the code with an information flow label that represents the privilege level of that code. A process at level  $\ell_{cur}$  can register a call gate at level  $\ell'$  as long as  $\ell_{cur} \sqsubseteq \ell'$ . Another process can then invoke a call gate, at which point the program counter is set to the entry point of the gate and  $\ell_{cur}$  is set to the level at which the gate was registered. To allow protected returns from call gates, invoking a call gate also pushes the previous program counter value and level of  $\ell_{cur}$  onto a hardware stack. The executing process can then invoke a return instruction to pop the stack, jumping to the old pc value and privilege level.

Call gates in HyperFlow are unique in that conventional hierarchical privilege levels are replaced with more general lattice-model information flow labels. By generalizing privilege levels, HyperFlow securely supports control transfers with fewer privilege changes than in a conventional processor while simultaneously providing more fine-grained separation of privilege. For example, in a system managed by a microkernel running on HyperFlow, a network driver can register a call gate at a security level  $\ell_{net}$  that is incomparable with other components of the microkernel. When an application wishes to send a packet over the network, it can directly invoke the call gate transferring immediately to  $\ell_{net}$ . In a conventional processor, the network driver can either run in supervisor mode, in which case the application must implicitly trust the entire kernel, or the network driver can run in userspace. In the second case, the application must first make a system call causing a transition to supervisor mode before the kernel delegates to the userspace driver. In this case, the application must both trust the kernel to delegate to the driver, and there is a performance penalty because of the extra privilege changes.

Using just a single level,  $\ell_{cur}$ , for a given process is often sufficient. However, other applications require the ability to operate on data within a space of information flow labels.

To permit flexibility with the label of executed instructions, HyperFlow allows the active process to move the level of  $\ell_{cur}$  within a space of labels bounded by  $\ell_{lwr}$  and  $\ell_{upr}$ . When setting the value of  $\ell_{cur}$ , we require  $\ell_{lwr} \sqsubseteq \ell_{cur} \sqsubseteq \ell_{upr}$ . For a process executing with a space of labels,  $C(\ell_{upr})$  and  $I(\ell_{upr})$  represent the most secret and most trusted information that the process can observe and affect respectively. On the other hand,  $C(\ell_{lwr})$  and  $I(\ell_{lwr})$  represent the least secrecy the process can claim it has observed and the least trustworthy information that it can be influenced by.

#### C. Instruction set extensions

HyperFlow introduces new instructions as well as new control and status registers. Security levels in HyperFlow are represented as a pair of confidentiality and integrity components as described in Section III. Levels  $\ell_{lwr}$ ,  $\ell_{cur}$ , and,  $\ell_{upr}$  are each stored in control and status registers (CSRs) and are accessed with conventional CSR instructions. The registers that store  $\ell_{lwr}$  and  $\ell_{upr}$  define the bounds for a process. To prevent a process from circumventing its own bounds, the bounds can only be modified when the processor is in the most public and trusted level, that is  $\ell_{cur} = (\bot, \top)$ . However,  $\ell_{cur}$  can be modified at any level as long as  $\ell_{lwr} \sqsubseteq \ell_{cur} \sqsubseteq \ell_{upr}$ .

The new instructions are summarized in Table I. The first column describes the instruction name and operands, the second column describes restrictions that must be satisfied when executing instructions, and the third column describes what the instruction does if the restrictions are satisfied. We overload the notation r to denote the value stored in register r. As before,  $\ell_r$  denotes the label associated with r and  $\mathcal{M}_{\ell}(a)$  denotes the label of the page containing address a.

The instructions DECLREG and ENDOREG downgrade registers. The DECLREG instruction declassifies the value stored in  $r_1$  to the confidentiality level stored in  $r_2$ , but it permits the declassification only if it is robust. The first restriction prevents implicit flows by ensuring that  $\ell_{cur}$  can write to the new level of  $r_1$ . The second restriction ensures that  $r_1$  can be robustly declassified from  $\ell_{r_1}$  to  $(r_2, I(\ell_{r_1}))$ .

The last restriction is more subtle - it prevents potential information flow violations that might be caused by the use of  $r_2$  as an argument. The register labels and memory labels are fully public and fully trusted. In most work on secure information flow, labels are public and trusted; otherwise, merely inspecting the labels releases information, and if the labels are not trusted, it is hopeless to rely on them for security. Because this instruction allows the value stored in  $r_2$  to influence a label, it must be permitted to influence fully public and trusted data. A natural way to ensure this is to simply require that  $\ell_{r_2} = (\bot, \top)$ . However, this restriction would often require extra instructions to first downgrade  $r_2$  before downgrading  $r_1$ . Instead, we enforce a less restrictive, but equally secure condition—it must be possible to downgrade  $r_2$  to  $(\bot, \top)$  using robust declassifications and transparent endorsements. This relaxed restriction does not weaken security because when the restriction on the label of  $r_2$  holds, it is always possible to first downgrade the label of  $r_2$ .

The instruction RSTREG allows a process to reclaim a register without downgrading by setting the level of the register  $r_1$  to  $\ell_{cur}$ . In order to avoid possibly downgrading the value stored in  $r_1$ ,  $r_1$  is cleared. Because this instruction takes no arguments other than  $r_1$ , and it happens unconditionally, no restrictions on this instruction are necessary. This instruction is useful for easily resetting the labels of registers because it does not impose any restrictions.

The LWDWN instruction works like a normal load word instruction, but it relaxes the restrictions on information flow labels. It permits the load if the value of the page from which the data is loaded could be downgraded to the label of the destination register, and to  $\ell_{cur}$ . Similarly, SWDWN works like a store instruction that permits the store if the register contents could be downgraded to the label of the destination page. Both instructions are useful for interprocess communication via shared memory.

The memory levels can be reset by totally trusted and public software through a SETMEM instruction, which takes two arguments: the page-aligned physical address in register  $r_1$  and confidentiality and integrity components in  $r_2$ . SETMEM sets  $\mathcal{M}_\ell(m)$  to r, where r is the value stored in r. The SETMEM instruction can only be executed when  $\ell_{cur} = (\bot, \top)$ . Trustworthy software that uses this instruction should clear the contents of the page to prevent implicit downgrades.

Entire pages can also be declassified/endorsed by user-space applications through the DECLMEM and ENDOMEM instructions, which are similar to SETMEM except that they require the changes in memory levels to be robust/transparent as in DECLREG and ENDOREG. As with DECLREG and ENDOREG, information flow violations through labels are also prevented by requiring that the arguments that influence labels can be downgraded securely.

The REGLGATE instruction registers a new call gate with a pc value of  $r_1$  and a label of  $r_2$  by adding it to a table T, that stores call gates by mapping pc values to labels. The first restriction,  $(\ell_{cur} \sqcup \ell_{r_1} \sqcup \ell_{r_2}) \sqsubseteq r_2$ , checks that the process creating the gate and the arguments from which the gate is constructed are no more secret and are at least as trusted as the label of the gate. The entries in the call gate table are public and trusted (though the labels of individual gates may be more restrictive), because processes that attempt to use call gates must be able to see whether or not they exist. Therefore, the last two restrictions check that the active process can downgrade the register arguments to public and trusted because they influence the creation of a call gate entry.

The LCALL and LCALLR instructions execute a call gate and have the same instruction formats as conventional JAL and JALR instructions. The LCALL instruction specifies the call-gate entry point with an immediate that is added to the current pc value, whereas the LCALLR instruction specifies the entry point by adding an immediate to a register argument. For both instructions, if the specified entry point is found in the call gate table, the address of the instruction following the call and the value of  $\ell_{cur}$  prior to the call are pushed to a hardware stack S for return addresses and labels. The processor then sets the

| Instruction         | Restrictions                                                                                                                                                                                                                                                                                                               | Behavior                                                                                                                                                                                               |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DECLREG R1, R2      | $ \begin{array}{c} \ell_{cur} \sqsubseteq (r_2, I(\ell_{r_1})) \\ \ell_{r_1} \xrightarrow{C} (r_2, I(\ell_{r_1})) \\ \ell_{r_2} \xrightarrow{\ell_{cur}} (\bot, \top) \\ \ell_{cur} \sqsubseteq (C(\ell_{r_1}), r_2) \end{array} $                                                                                         | $C(\ell_{r_1}) \leftarrow r_2$                                                                                                                                                                         |  |

| ENDOREG R1, R2      | $ \begin{array}{c} \ell_{cur} \sqsubseteq (C(\ell_{r_1}), r_2) \\ \ell_{r_1} \xrightarrow{I} (C(\ell_{r_1}), r_2) \\ \ell_{r_2} \xrightarrow{\ell_{cur}} (\bot, \top) \end{array} $                                                                                                                                        | $I(\ell_{r_1}) \leftarrow r_2$                                                                                                                                                                         |  |

| RSTLREG R1          | None.                                                                                                                                                                                                                                                                                                                      | $ \begin{array}{l} \ell_{r_1} \leftarrow \ell_{cur} \\ r_1 \leftarrow 0 \end{array} $                                                                                                                  |  |

| LWDWN R2, IMM(R1)   | $\begin{split} \mathcal{M}_{\ell}(r_1 + \texttt{IMM}) & \xrightarrow[\ell_{cur}]{} \ell_{r_2} \\ \mathcal{M}_{\ell}(r_1 + \texttt{IMM}) & \xrightarrow[\ell_{cur}]{} \ell_{cur} \\ \ell_{r_2 \sqcup \ell_{cur}} & \xrightarrow[\ell_{cur}]{} \mathcal{M}_{\ell}(r_1 + \texttt{IMM}) \end{split}$                           | $r_2 \leftarrow \mathcal{M}(r_1 + \mathtt{IMM})$                                                                                                                                                       |  |

| SWDWN R2, IMM(R1)   | $\ell_{r_2 \sqcup \ell_{Cur}} \xrightarrow[\ell_{Cur}]{\mathcal{M}_{\ell}(r_1 + \text{IMM})}$                                                                                                                                                                                                                              | $\mathcal{M}(r_1 + \mathtt{IMM}) \leftarrow r_2$                                                                                                                                                       |  |

| SETMEM R2, IMM(R1)  | $\ell_{cur} = (\bot, \top)$                                                                                                                                                                                                                                                                                                | $\mathcal{M}_{\ell}(r_1) \leftarrow r_2$ $\mathcal{M}(r_1) \leftarrow 0$                                                                                                                               |  |

| DECLMEM R2, IMM(R1) | $ \begin{split} &\ell_{cur} \sqsubseteq (r_2, I(\mathcal{M}_{\ell}(r_1 + \text{IMM}))) \\ &\mathcal{M}_{\ell}(r_1 + \text{IMM}) \xrightarrow{C} (r_2, I(\mathcal{M}_{\ell}(r_1 + \text{IMM}))) \\ &\ell_{r_2} \xrightarrow[\ell_{cur}]{} (\bot, \top) \\ &\ell_{r_1} \xrightarrow[\ell_{cur}]{} (\bot, \top) \end{split} $ | $C(\mathcal{M}_{\ell}(r_1)) \leftarrow r_2$                                                                                                                                                            |  |

| ENDOMEM R2, IMM(R1) | $ \begin{array}{c} \ell_{cur} \sqsubseteq (C(\mathcal{M}_{\ell}(r_1)), r_2) \\ \mathcal{M}_{\ell}(r_1 + \mathtt{IMM}) \xrightarrow{I} (C(\mathcal{M}_{\ell}(r_1 + \mathtt{IMM})), r_2) \\ \ell_{r_2} \xrightarrow{\ell_{cur}} (\bot, \top) \\ \ell_{r_1} \xrightarrow{\ell_{cur}} (\bot, \top) \end{array} $               | $I(\mathcal{M}_{\ell}(r_1)) \leftarrow r_2$                                                                                                                                                            |  |

| REGLGATE R1, R2     | $ \begin{array}{c} \iota_{cur} \\ (\ell_{cur} \sqcup \ell_{r_1} \sqcup \ell_{r_2}) \sqsubseteq r_2 \\ \ell_{r_2} \xrightarrow[\ell_{cur}]{} (\bot, \top) \\ \ell_{r_1} \xrightarrow[\ell_{cur}]{} (\bot, \top) \end{array} $                                                                                               | $T[r_1] \leftarrow r_2$                                                                                                                                                                                |  |

| LCALL IMM           | None.                                                                                                                                                                                                                                                                                                                      | $\begin{split} S &\leftarrow S :: (\text{pc} + 4, \ell_{cur}, \ell_{lwr}, \ell_{upr}) \\ \text{pc} &\leftarrow \text{pc} + \text{IMM} \\ \ell_{cur} &\leftarrow T[\text{pc} + \text{IMM}] \end{split}$ |  |

| LCALL IMM(R1)       | $\ell_{r_1} \xrightarrow[\ell_{cur}]{} (\bot, \top)$                                                                                                                                                                                                                                                                       | $\begin{split} S \leftarrow S :: (\text{pc} + 4, \ell_{cur}, \ell_{lwr}, \ell_{upr}) \\ \text{pc} \leftarrow r_1 + \text{IMM} \\ \ell_{cur} \leftarrow T[r_1 + \text{IMM}] \end{split}$                |  |

| LRET                | None.                                                                                                                                                                                                                                                                                                                      | $ \begin{array}{l} (pc, \ell_{cur}, \ell_{lwr}, \ell_{upr}) \leftarrow \texttt{tail}(\texttt{S}) \\ S \leftarrow \texttt{head}(\texttt{S}) \end{array} $                                               |  |

| SETBOUNDS           | $\ell_{cur} = (\bot, \top)$                                                                                                                                                                                                                                                                                                | $\begin{aligned} &\ell_{cur} \leftarrow \ell_{ncur} \\ &\ell_{lwr} \leftarrow \ell_{nlwr} \\ &\ell_{upr} \leftarrow \ell_{nupr} \end{aligned}$                                                         |  |

TABLE I

NEW INSTRUCTIONS ADDED IN HYPERFLOW.

pc value to the entry point of the gate and sets  $\ell_{cur}$  to the label of the gate. If the gate does not exist, the instruction is converted to a NOP. The instruction LRET pops the stack S and returns to the most recent pc value and label.

Finally, the SETBOUNDS instruction permits software that is fully public and fully trusted to set the label bounds. There are CSRs called  $\ell_{ncur}$ ,  $\ell_{nlwr}$ ,  $\ell_{nupr}$  that privileged software can read and write normally. The SETBOUNDS instruction atomically copies these CSRs to  $\ell_{cur}$ ,  $\ell_{lwr}$ , and  $\ell_{upr}$  respectively in a single cycle. This instruction is necessary, because writing to an individual bound register might otherwise temporarily violate the invariant,  $\ell_{lwr} \sqsubseteq \ell_{cur} \sqsubseteq \ell_{upr}$ .

## D. Semantic changes to existing instructions

In addition to the new instructions, HyperFlow also changes the semantics of existing instructions in order to ensure that the policies described by the information flow labels are enforced. To enforce these polices, a set of invariants must hold for each instruction that is executed. The invariants depend on the kind

| Instruction Type         | Invariant                                                                                                                                 |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Load instructions        | $\ell_{r_a} \sqcup \mathcal{M}_{\ell}(m) \sqcup \ell_{cur} \sqsubseteq \ell_{r_d} \\ \wedge \mathcal{M}_{\ell}(m) \sqsubseteq \ell_{cur}$ |  |

| Store instructions       | $\ell_{r_a} \sqcup \ell_{r_v} \sqcup \ell_{cur} \sqsubseteq \mathcal{M}_{\ell}(m)$                                                        |  |

| Execute unit             | $\ell_{r_{s1}} \sqcup \ell_{r_{s2}} \sqcup \ell_{cur} \sqsubseteq \ell_{r_d}$                                                             |  |

| Value-dependent branches | $\ell_{r_{s1}} \sqcup \ell_{r_{s2}} \sqsubseteq \ell_{cur}$                                                                               |  |

| All instructions         | $\mathcal{M}_{\ell}(m_i) \sqsubseteq \ell_{cur}$                                                                                          |  |

TABLE II INSTRUCTION INVARIANTS ENFORCED BY HYPERFLOW.

of instruction being executed. For example, different invariants hold for arithmetic instructions and memory instructions. Table II summarizes these invariants. The invariants serve two purposes: 1) to implement memory protection, and 2) to ensure that the labels of the registers and memory pages accurately capture the secrecy and integrity of the data they protect.

Memory protection is enforced by ensuring that when a process with label  $\ell_{cur}$  loads from a page m,  $\mathcal{M}_{\ell}(m) \sqsubseteq \ell_{cur}$ ,

to prevent reads that would violate security. This is explicitly enforced on loads. On stores to m, we require  $\ell_{cur} \sqsubseteq \mathcal{M}_{\ell}(m)$  which is subsumed by the invariant enforced by store instructions listed in the table.

For all instructions regardless of type, HyperFlow must enforce the condition  $\mathcal{M}_{\ell}(m_i) \sqsubseteq \ell_{cur}$ , where  $m_i$  is the memory page where the instruction is fetched from. This prevents information from leaking to the process via the fetched instruction.

The rest of the invariants preserve the accuracy of the information flow labels. For load instructions, condition

$$\ell_{r_a} \sqcup \mathcal{M}_{\ell}(m) \sqcup \ell_{cur} \sqsubseteq \ell_{r_d}$$

must also hold, where  $r_a$  is the source register that contains the base address and m is the page which contains the data being loaded. This invariant ensures that the level of the destination register accurately reflects the level of the data it stores. Similarly, store instructions require

$$\ell_{r_a} \sqcup \ell_{r_v} \sqcup \ell_{cur} \sqsubseteq \mathcal{M}_{\ell}(m)$$

where  $r_v$  is the register that contains the value being written, and m is the page being written to. This invariant ensures that the policy described by the level of the page being written to is also not violated by the data being written to the page or by the address.

Computation instructions such as arithmetic and logical instructions, multiplication and division, and floating-point instructions, perform a computation on arguments and write the result back into a destination register. For these instructions,

$$\ell_{r_{s1}} \sqcup \ell_{r_{s2}} \sqcup \ell_{cur} \sqsubseteq \ell_{r_d}$$

must hold, where  $r_{s1}$  and  $r_{s2}$  are the source registers and  $r_d$  is the destination register. The data is influenced by the values of both the source registers (which are bounded by  $\ell_{r_{s1}}$  and  $\ell_{r_{s2}}$ ) as well as the process causing the instruction to execute (which is bounded by  $\ell_{cur}$ ).

Value-dependent control-flow instructions such as conditional branches must enforce the invariant

$$\ell_{r_{s1}} \sqcup \ell_{r_{s2}} \sqsubseteq \ell_{cur}$$

.

Because  $\ell_{cur}$  represents the security level of the current control flow (program counter) as well as the security level of a process, a change to the program counter can only be affected by information that can flow into  $\ell_{cur}$ . This invariant prevents branch instructions that would violate the information flow policy.

#### V. HYPERFLOW MICROARCHITECTURE AND LABELING

This section describes the microarchitecture extensions necessary for HyperFlow and how they are be labeled in the secure HDL. The HyperFlow instruction set architecture can be realized by many implementations and microarchitectures. Here, we discuss our prototype implementation based on the RISC-V Rocket Chip processor. The HyperFlow implementation includes many advanced microarchitecture features such

as a pending store buffer, pipelined caches, branch prediction, virtual memory, and atomic memory operations, which were not studied in previous information-flow-secured processor designs. Appendix C provides more details on the design trade-offs we considered to make the HyperFlow implementation pass the information flow security analysis performed by the type system, and how the process of implementing hardware with a security-typed HDL differs from that of conventional hardware designs.

#### A. Labels in the core and label bypassing

In the processing core, the security label of the current process  $(\ell_{cur})$  is stored in a new control status resister (CSR). The confidentiality and integrity components,  $C(\ell_{r_i})$  and  $I(\ell_{r_i})$ , of general purpose registers  $r_i$  are stored in register banks adjacent to the registers. These label registers can be modified only by the DECLREG and ENDOREG instructions, which are guarded by logic that checks the non-malleability conditions, and the RSTLREG instruction which can only set the label of a register to  $\ell_{cur}$ .

The HyperFlow core supports data bypassing. To function correctly, the security labels must be bypassed with the data. For immediate values, the bypassed label is  $\ell_{cur}$ . For a value from a register or a cache, its label travels with the bypassed data. The bypassed labels are themselves labeled with  $\ell_{cur}$  because they might be stalled or updated by the current process.

# B. Memory and cache labels

The memory page labels  $(\mathcal{M}_\ell(m))$  are stored in an on-chip table that maps page numbers to labels. Initially, every page is mapped to the most public and trusted label  $C(\bot) \land I(\top)$ . The SETMEM, DECLMEM, and ENDOMEM instructions issue memory transactions that modify the memory label table. The current security label  $(\ell_{cur})$  is attached to each memory transaction so that information flow and downgrading can be checked in the memory system. For a system with large off-chip memory, the memory page labels may be stored in off-chip memory along with data.

In the data cache, a data label is added to each cache line to track the memory label for the physical address stored in the cache line. The memory label is appended to a cache refill transaction from memory. The data cache is blocking, so memory tags are always brought into the cache before any data is modified or returned to the core. For a load, the cache only returns data if the data label of the accessed cache line flows to  $\ell_{cur}$ . The core updates the destination register only if the label of the returned cache data flows to the label of the destination register. The security of a store is enforced by checking that the label of a pending store buffer entry flows to the label of the cache line, and that the label of a memory transaction flows to the memory page label.

The LWDWN instruction may be used to load a value with downgrading and performs three non-malleability checks. The cache checks that the value can be downgraded to  $\ell_{cur}$ . Then, the core checks that the data label of the cache response can

be downgraded to the destination register's label; two checks are added, one near the bypassed data and the other near the register file writeback.

#### C. Timing-channel protection

$\ell_{cur}$  is also used as a timing label to prevent timing channels through microarchitectural state. That is,  $C(\ell_{cur})$  is an upper bound on the level of secrecy that the process is permitted to observe by measuring timing. Any microarchitectural state that influences the timing of instructions is protected by  $\ell_{cur}$ . Cache entries, in-flight instructions and cache transactions, translation-lookaside buffer (TLB) and page table walker (PTW) entries, and branch predictor state are examples of state that influences instruction timing. Because the security type system in ChiselFlow enforces timing-sensitive non-interference, timing channels must be removed for the hardware to type-check.

When the value of  $\ell_{cur}$  moves downwards in the lattice, the level of secrecy that the process can observe is decreasing. HyperFlow must prevent secrets owned by the previous level of  $\ell_{cur}$  from leaking to the new one. The processor pipeline is drained to prevent high instructions from stalling low instructions as well as other subtle timing channels through register bypassing. In-flight transactions in pipelined caches are also drained when  $\ell_{cur}$  is lowered.

The pending store buffer in the data cache also introduced a subtle timing channel that we did not initially expect. Outstanding cache-write requests in the pending store buffer are serviced opportunistically when there is no in-flight read request. The store buffer can cause a stall either when the content of the buffer might have a read-after-write hazard or when the buffer is full. To prevent a timing channel, we enforce that all entries of the pending store buffer must have the same label, and the buffer is drained before lowering  $\ell_{cur}$ .

Caches may also cause timing channels when they are shared among security levels. For instruction caches, the timing channel can be removed by simply clearing and invalidating cache lines when lowering  $\ell_{cur}$ . However, in the data cache, dirty cache lines must be written back when they are evicted, and cannot be simply invalidated. In our implementation, we require software to issue a cache flush instruction to write-back dirty cache blocks before executing an instruction to lower  $\ell_{cur}$ . When  $\ell_{cur}$  is lowered, the data cache is invalidated in a single clock cycle.

While our prototype implementation uses flushing to remove cache timing channels, cache partitioning can also be used to lower the flushing overhead on a label change. With partitioned caches, each partition can have a register for its own security label. Then, the logic for a cache read only searches partitions with labels  $\ell_P$  such that  $\ell_P \sqsubseteq \ell_{cur}$ . When the security label of a partition changes downwards in the lattice, only that partition will need to be invalidated.

HyperFlow has both *branch prediction*, which predicts whether or not branches are taken, as well as *branch target prediction*. The branch target predictor (BTB) in HyperFlow

is fully-associative. The branch history table (BHT) has two-bit states per index and a global history register. Prior work has demonstrated that both forms of branch prediction create timing channels that are capable of leaking secrets from Intel SGX enclaves [?]. To prevent timing channels, when  $\ell_{cur}$  moves downward, the BTB is invalidated and cleared, the BHT is cleared, and the global history register is reset.

#### D. Virtual memory

The HyperFlow implementation includes support for virtual memory. While HyperFlow protects memory using memory labels, the virtual memory system provides a familiar interface to the software and permits software to run on HyperFlow mostly unmodified. Virtual memory support includes instruction and data TLBs as well as a hardware page table walker (PTW). TLBs influence timing because they are caches of recently used Level-1 (L1) page table entries (PTEs). L1 PTEs store mappings from virtual to physical addresses. The PTW serves as a cache of L2 PTEs, which store pointers to L1 PTEs. The TLB and PTW state are labeled with  $\ell_{cur}$ , and the state is cleared when  $\ell_{cur}$  moves downward in the lattice.

Because the TLB and PTW state is labeled with  $\ell_{cur}$ , PTEs must be stored in a memory page with a label that flows to  $\ell_{cur}$ . This restriction must be satisfied by the software that manages the page tables. One simple option is to label the memory pages for page tables with  $(C(\bot), I(\top))$ , which is the least-restrictive information-flow label. The page table can also be stored in pages with more restrictive labels as long as they flow into the processes that use the page table.

# E. Atomic memory operations

Like the baseline processor it extends, HyperFlow supports atomic memory operations (AMOs). AMOs are critical for operating system implementations because they are needed to implement synchronization primitives. AMOs are implemented by buffering both operands into different slots of the pending store buffer in the data cache before buffering the result back into the first slot of the pending store buffer. Implementing AMOs securely is challenging because the operands are buffered-in over multiple clock cycles, meaning they might have different timing labels, and because they are computed from operands that might also have different data labels. Because both AMO operands are buffered-in by the same instruction, both operands have the same timing label. To reduce the number of ports in the AMO execute unit, both operands, and therefore the output, are required to have the same label.

#### VI. EVALUATION

We developed a prototype implementation of HyperFlow as an extension to a single-core configuration of the RISC-V Rocket Chip processor. This is a more full-featured processor than those previously implemented with statically checked information-flow [14], [20], [21], [43]. The prototype implementation label-checks with ChiselFlow and successfully runs all of Rocket Chip's ISA and application unit tests.

## A. Processor features

The processor is pipelined, with branch prediction and branch target prediction. The branch history table has 2 bits of state per entry and a global history register. The branch target predictor is fully associative. The execution units include an ALU, a multi-cycle multiplier, and a floating-point unit (FPU).

The FPU is implemented as an independent coprocessor that receives instructions from the main processor, but it has its own independent instruction-decode unit, floating-point register file, and pipeline. The FPU sends requests to the memory hierarchy independently of the main processor.

The processor has four hierarchical protection rings, and a 32-bit virtual address space divided into 4KiB pages. The baseline processor has L1 instruction and data caches each with 64 sets and 4 ways. Both L1 caches have 2 pipeline stages. The data cache has a two-slot pending store buffer. Both caches are virtually indexed and physically tagged. The caches include cache controllers. Separate instruction and data TLBs store level-1 page table entries for each cache. A single hardware page-table walker refills both TLBs on misses and caches recently-used level-2 page-table entries.

Many of these micro-architectural features have been absent in prior information-flow secured processor implementations. To the best of our knowledge, HyperFlow is the first to include, TLBs, a PTW, branch and branch target prediction, and a pending store buffer. Most of these features introduce subtle timing channels that we address. HyperFlow is also the first to include data bypassing with fine-grained information flow labels. This necessitates dynamic label bypassing, which we must also label-check. The prototype implementation of HyperFlow includes all of the aforementioned features as well as the ISA and microarchitectural extensions described in Sections IV and V. The HyperFlow prototype does not include hardware accelerators and relies on a hard-wired memory controller on an FPGA.

## B. Developer effort

HyperFlow was implemented by a single developer requiring roughly eight person-months of effort. While the existing Chisel implementation of the RISC-V Rocket chip provides most of the hardware functionality described above, it contains many timing channels. Much of the work required modifying the microarchitectural design to eliminate these timing channels, especially in the instruction and data cache pipelines, virtual memory hardware, and multiplier. Aside from, eliminating timing channels, many of the other hardware features, such as bypassing, required rewriting of the hardware to make it amenable to program analysis, even though the functionality was not changed. The labeling support provided by ChiselFlow was essential for removing timing channels correctly. By contrast, it was straightforward to extend the architecture with new instructions for managing labels, downgrading, and call gates - label-checking these features did not pose significant challenges beyond those of conventional hardware implementation. Label-checking many other features already present in RISC-V imposed no additional effort for label-checking; for example, the instruction expansion units and additional decode logic for compressed instructions labelcheck trivially. Label inference significantly reduced required developer effort.

#### C. Uses of downgrades

The RTL code for HyperFlow performs downgrades at various points; these downgrades are checked for nonmalleability by the ChiselFlow type system. Our formal results imply that insecure information flows can only arise because of these downgrades, which should therefore be inspected carefully. All but one downgrade is statically checked to be nonmalleable by the type system. Table III summarizes the uses of RTL-level downgrades. The first column shows the ISA-visible event to which the downgrade is tied, the second column states the number of downgraded expressions in the RTL code, and the third gives a brief description of what is downgraded. For all downgrades other than downgrades of data caused by explicit downgrade instructions, both an endorsement and a declassification happen.

We expand upon these descriptions here. When the processor resets (1), the register file tags are all initialized to  $(\bot, \top)$ . This initialization requires explicit writes to the tags because the register file labels are implemented as a sequential memory that can be synthesized as a BRAM on an FPGA. However, this initialization is secure because the processor is initially public and trusted and boots public and trusted code. For convenience, copies from the FPU to the integer register file (2) are automatically downgraded if the labels of the data coming out of the FPU can be nonmalleably downgraded. When  $\ell_{cur}$  moves downwards in the lattice (3), it is possible for a single outstanding cache coherence transaction to remain in a pending transaction buffer, causing timing interference. We resolve this with a downgrade, but nothing is leaked if the software is written as described in Section IV: prior to lowering  $\ell_{cur}$ , the software should issue a cache flush instruction to flush any buffered coherence transaction. When a memory transaction is issued (4), the data used to compute the address is downgraded to  $\ell_{cur}$  because the address affects the timing of the cache transaction; this downgrade is for convenience because the address can otherwise be downgraded with an instruction. The label of the address is still protected by the data label, and so the store invariant in Table II is enforced by the data label. To permit the use of performance counters, writes to the CSR file (5) are downgraded to  $\ell_{cur}$ .

The downgrading instructions (DECLREG, ENDOREG, LWDWN, SWDWN DECLMEM, and ENDOMEM) downgrade the stored data and the arguments to the instructions (6–9). These downgrades are done under a conditional statement that checks that these values are downgraded nonmalleably. As described in Section IV, the arguments are also downgraded to  $(\bot, \top)$  because the arguments influence changes to public and trusted labels – this downgrade is also guarded by a nonmalleability check. The labels of the arguments are also bypassed, and bypassed labels are labeled  $\ell_{cur}$ . Because the bypassed labels are inspected by the nonmalleability check, which influences whether or

|    | When is Information Downgraded | Number of Downgrades | What is Downgraded                                                  |  |  |  |

|----|--------------------------------|----------------------|---------------------------------------------------------------------|--|--|--|

| 1  | On Reset                       | 1                    | Register tags (for initialization)                                  |  |  |  |

| 2  | FPU to Int instructions        | 1                    | Values copied from the FPU to integer registers (when nonmalleable) |  |  |  |

| 3  | $\ell_{cur}$ lowers            | 2                    | Presence of one outstanding finish coherence transaction            |  |  |  |

| 4  | Memory instructions            | 1                    | Address is downgraded to $\ell_{cur}$                               |  |  |  |

| 5  | CSR file writes                | 1                    | Data written to CSR file is downgraded to $\ell_{cur}$              |  |  |  |

| 6  | DECLREG, ENDOREG               | 7(1 + 3  each)       | Register contents, control signals, arguments                       |  |  |  |

| 7  | LWDWN                          | 2                    | RF writeback data, dcache bypass data                               |  |  |  |

| 8  | SWDWN                          | 1                    | P-store buffer data                                                 |  |  |  |

| 9  | DECLMEM, ENDOMEM               | 9 (1 + 4 each)       | Page contents, control signals, arguments                           |  |  |  |

| 10 | RSTLREG                        | 1                    | Control signal                                                      |  |  |  |

| 11 | REGLGATE                       | 8                    | Control signals, arguments, pipelined data labels                   |  |  |  |

| 12 | LCALL, LCALLR                  | 3                    | Control signal, arguments, pc value                                 |  |  |  |

| 13 | LRET                           | 1                    | Control signal                                                      |  |  |  |

| 14 | MMIO Responses                 | 1                    | MMIO response transaction data                                      |  |  |  |

|    | TABLE III                      |                      |                                                                     |  |  |  |

USES OF DOWNGRADES IN HYPERFLOW.

not the downgrade happens, the labels of the bypassed labels are also downgraded from  $\ell_{cur}$  to  $(\bot, \top)$ . The control signals that induce the downgrades are also downgraded to  $(\bot, \top)$  – this downgrade is always nonmalleable because these control signals are labeled  $\ell_{cur}$ . The LWDWN instruction downgrades the data in two places in the core: the bypass data from the cache and the register file writeback data from the cache. The SWDWN instruction downgrades the stored data from the label in the pending store buffer to the label indicated by the memory tags that are stored in the cache. Neither LWDWN nor SWDWN changes the valuation of any labels, so these instructions do not induce downgrades of control signals or arguments.

Similarly, for instructions RSTLREG, REGLGATE, LCALL, LCALLR, and LRET (10–13), control signals are downgraded because these instructions affect public and trusted state. The REGLGATE instruction also includes a nonmalleability check on pipelined labels. The LCALL and LCALLR instructions store the old pc value in a public and trusted stack, so the pc is downgraded from  $\ell_{cur}$  to  $(\bot, \top)$ .

Finally, one downgrade endorses and declassifies data from memory-mapped IO devices (14). This downgrade is not in general nonmalleable because we do not provide protection for or from memory-mapped IO devices.

# D. Uses of dynamic checks

Dynamic checks are alternatives to downgrades. They are dynamic label comparisons that are written to establish some invariant. They are preferable to downgrades because they do not weaken security. However, care must be taken because dynamic checks should only be used when it is expected that the invariant can never be violated. Dynamic checks are used in HyperFlow to establish that  $\ell_{lwr} \sqsubseteq \ell_{cur}$ . This invariant is established in the control and status register (CSR) file where those registers are stored. However, the fact that this invariant is true is not visible in other components outside the CSR file. Another use of dynamic checks is to prevent timing channels caused by floating-point computation. Because the FPU computes on register values, and the time taken to finish a floating-point computation is data-dependent, the stall signals from the FPU are also data-dependent. The pipeline register stall signals in HyperFlow are labeled with  $\ell_{cur}$ . We use a dynamic check that hides the stall signals from the FPU when

the data values do not flow to  $\ell_{cur}$ . Another dynamic check is used to convince the type system that the bypass value from the data cache does not cause timing channels; this dynamic check forces the bypass value from the cache to 0 if the timing label from the data cache response does not flow to  $\ell_{cur}$ , but permits the actual data value to be returned otherwise. In practice, this dynamic check does not cause a functional error because when  $\ell_{cur}$  is lowered, the data cache pipeline is stalled and cannot emit responses. Both the regular data cache bypass value and a downgraded bypass value produced by LWDWN are covered b the dynamic check.

# E. RTL synthesis results

We synthesized the baseline processor and HyperFlow using Vivado v2016.2 targeting the 7z020clg484-1 FPGA found on the Zedboard Zynq 7000 development board. The baseline processor uses 34,508 LUTs (64.9%) on the FPGA, whereas HyperFlow uses 40,205 LUTs (75.6%), a LUT utilization overhead of 16.5%. The baseline processor uses 13 (9%) of the block RAM tiles whereas HyperFlow utilizes 19.5 (14%). The majority of the utilization overhead is due to the security tags stored with each cache entry, the tag table that associates tags with memory pages, and dynamic label comparisons, which are used for either access controls or dynamic checks. For both the baseline processor and HyperFlow, Vivado is able to meet a target clock frequency of 25MHz. For both designs, the critical path is through the FPU multiplier, so we expect that the minimum clock period is the same for both designs.

# F. CPI Results

Although HyperFlow has no clock frequency overhead, there is performance overhead for timing channel protection. We measured the cycles per instruction (CPI) for HyperFlow when executing the RISC-V benchmark suite compared to the baseline RocketChip processor. For the HyperFlow processor, the processor executes with the same security level during the entire execution of the program. The results are summarized in Table IV. HyperFlow incurs a performance penalty because unlike RocketChip, the multiplier unit always executes in the worst case number of cycles. This performance penalty can be removed by disallowing multiplications of operands with data labels that do not flow to  $\ell_{cur}$ . The mm benchmark

| Benchmark name | HyperFlow CPI | RISC-V CPI | Percent Overhead |  |  |

|----------------|---------------|------------|------------------|--|--|

| mm             | 1.089         | 1.063      | 2.4%             |  |  |

| spmv           | 1.748         | 1.678      | 4.2%             |  |  |

| median         | 1.631         | 1.284      | 27%              |  |  |

| multiply       | 1.899         | 1.115      | 69%              |  |  |

| qsort          | 1.542         | 1.531      | 0.7%             |  |  |

| towers         | 1.052         | 1.030      | 2.14%            |  |  |

| vvad           | 1.161         | 1.094      | 6.12%            |  |  |

| dhrystone      | 1.206         | 1.187      | 1.6%             |  |  |

| TABLE IV       |               |            |                  |  |  |

PERFORMANCE RESULTS

is matrix-matrix multiply, spmv is double-precision sparse matrix vector multiply, median is a median filter, multiply does multiplications, qsort does quicksort on an array of integers, towers solves a towers of Hanoi puzzle, vvad adds two vectors, and dhrystone is the classic synthetic benchmark. The benchmark with the highest overhead is multiply, naturally. The geometric mean overhead is 12.4%.

HyperFlow also introduces performance overhead through hardware state that is flushed or invalidated on label changes, but these occur infrequently—when the active process changes via a context switch, or when the application information through instructions. The time between context switches is on the order of tens of milliseconds, so this overhead should be amortized over execution.

#### G. Usability

HyperFlow intends to support necessary communication among mutually distrusting principals in an environment managed by an operating system. HyperFlow also supports the expressive information flow label models that have been proposed for prior operating systems and languages for information flow control. In this section, we demonstrate that HyperFlow supports shared memory interprocess communication, communication through registers for system calls, and enforcement of rich information flow policies.

We demonstrate how labels represented in the FLAM model can be expressed as hypercube labels and enforced. The flow-limited authorization model (FLAM) is a recent model that supports decentralized security policies [2]. To illustrate the usability of the HyperFlow architecture, we implemented a simple application with a decentralized information flow control (DIFC) policy expressed in FLAM originally by Myers and Liskov [?]. DIFC policies allow communication among mutually-distrusting principals [5], [12], [26], [41].